10bit 60MsPs 15mW流水線ADC的設計

0 引言

模數轉換器是現代數字通信系統中十分重要的單元。與模擬信號相比,數字信號具有便于存儲、轉移、保真度和可靠性高等優點。但是因為人們所處的世界是連續的模擬環境,其中所有(物理、化學、生物等)信號都是模擬的,這是數字電路無法直接處理的。因此,必須借助于ADC將從外部采集來的模擬信號轉變成數字信號,才能由數字電路處理,然后再以適當的方式輸出。隨著無線通信系統和手持設備的快速發展,ADC的功耗已經成為ADC設計中的主要問題。特別是在移動電話、數碼相機、手持存儲設備等應用中,減小ADC的功耗已成為必然的趨勢。本文通過對比較器進行特殊的處理,去掉了ADC中的采樣保持電路,并且引入運放共享(op-amp shar-ing)技術,從而完成了一個分辨率為10bit、采樣頻率為60 MHz、功耗為15 mW的全差分流水線低功耗ADC的設計。

1 ADC第一級的設計

在傳統流水線ADC結構中,為了減小MDAC和比較器之間時鐘不匹配帶來的動態誤差,通常需要引入一個采樣保持電路來保證MDAC和比較器具有同樣的采樣電平。雖然,采樣保持器的引入可以很大程度的減小ADC的動態誤差。但是,為保證整個ADC的精度,采樣保持電路的精度必須高于ADC的要求。這就要求采樣保持電路中的運放必須有足夠高的增益和足夠大的帶寬,因此采樣保持器就成為整個ADC功耗最大的一個模塊,通常要消耗整個ADC器件1/5到1/4的功耗。

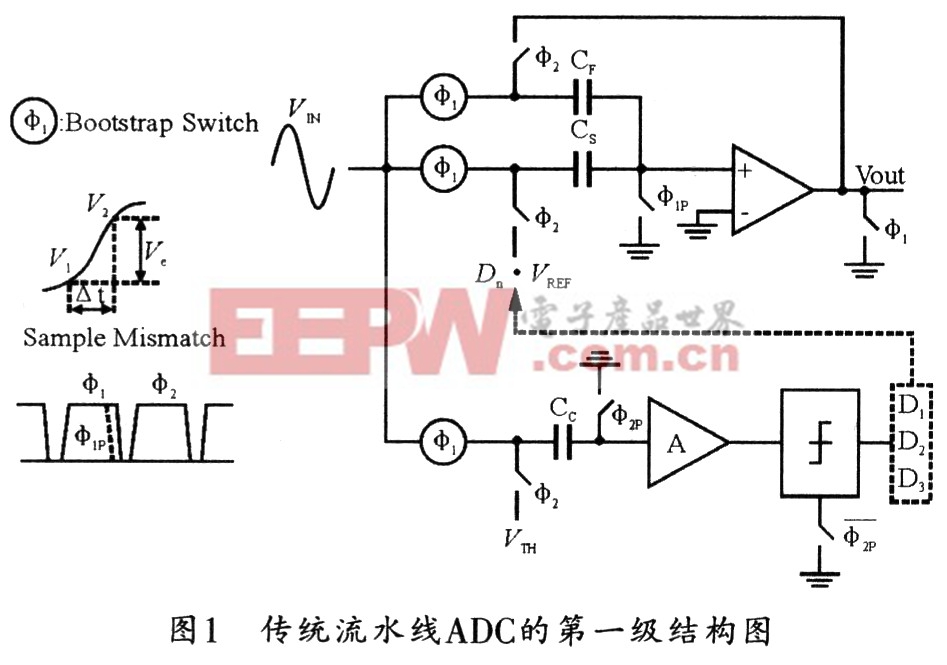

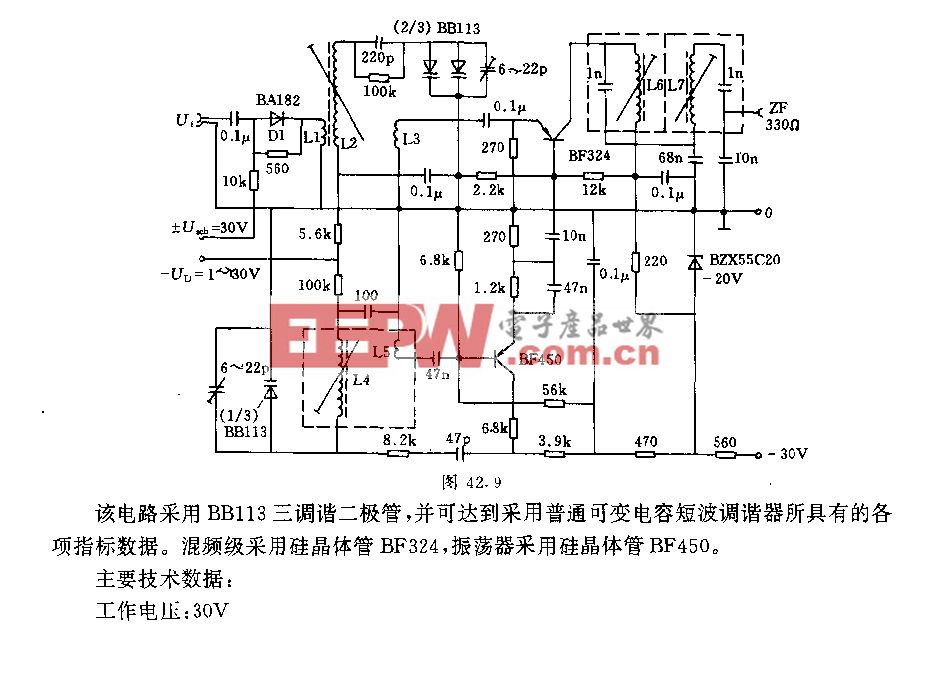

傳統無采樣保持電路ADC的第一級結構如圖1所示。在ψ2時刻,比較器對閾值電壓VTH進行采樣,與此同時,MDAC處于對余量電壓進行放大的狀態。當ψ1到來時,MDAC和比較器同時對模擬輸入信號進行采樣。MDAC在ψ1P下降沿采到V2,但是由于比較器前置放大器存在一個△t的延時,所以比較器實際采到并決定輸出比特值的電壓是在ψ1P下降沿前△t時刻采到的V1。換一句話說,由于前置放大器存在延時,比較器采到的電壓值要比V2早,故與V2存在一個Ve的差值。而Ve與輸入頻率、最大斜率等參數有關,其每級1.5 bit的傳遞函數如下式所示:

式中,Dn可取-1,0,1。它的誤差容忍范圍(即Ve的最大值)為1/4VREF。假設輸入信號為Vin=VREFsin(2πfint),fin為其輸入頻率,那么,它的最大斜率可以表示為:

|

|

所以,△t時間的不匹配所引入的Ve可以表示為2πfinVREF△t。可見,輸入越快,Ve越大。對于每級2.5 bit的ADC,Ve允許的最大值為1/8 Vref。

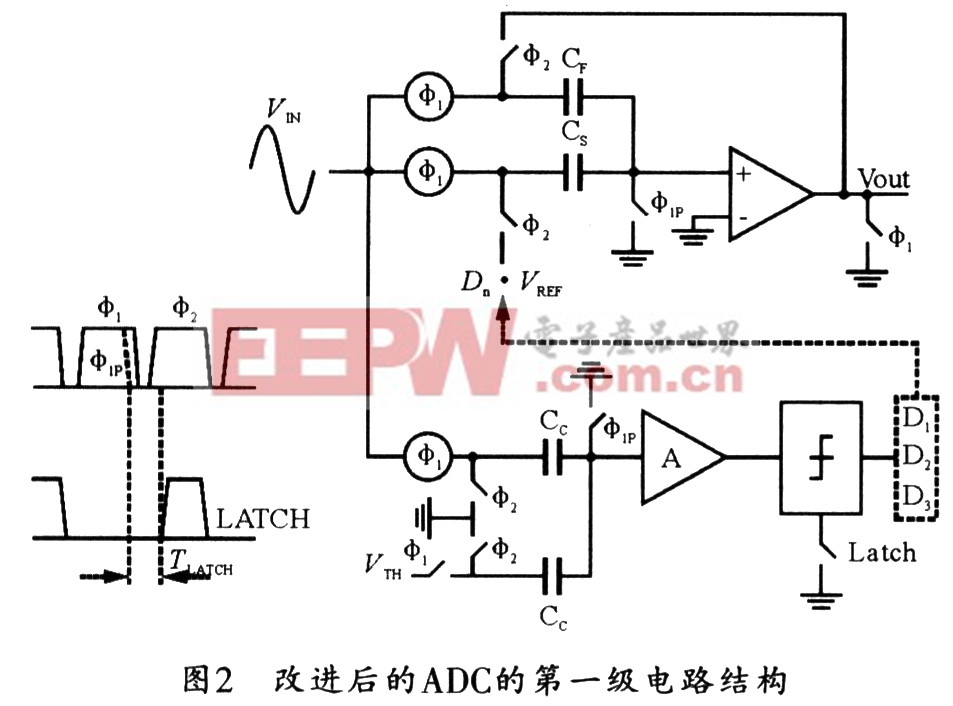

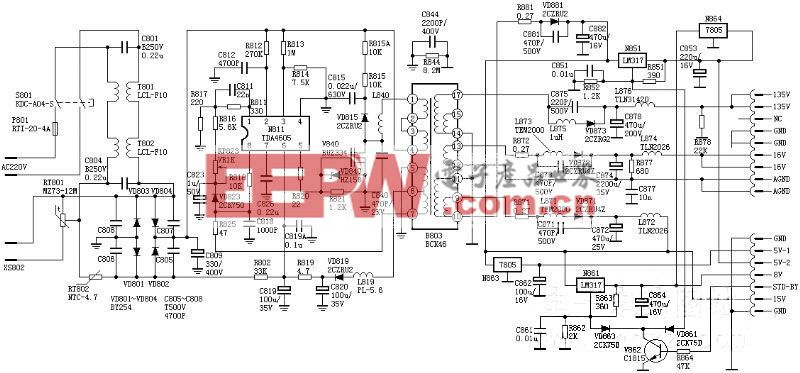

為了消除Ve,本設計中采用改進的ADC第一級結構,其電路如圖2所示。其中比較器有兩個分開的電容,在φ1時候,分別對信號和閾值電壓VTH進行采樣。φ1結束時,前置放大器有一段時間Tamp對φ1p下降沿采到的信號進行放大。這就避免了由于前置放大器延時所引入的△t,消除了Ve,因此也就提高了第一級電路的動態性能。

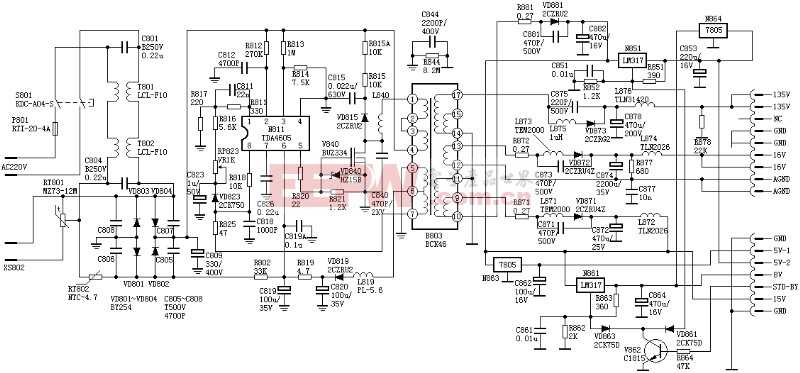

2 運放分享技術

流水線ADC是在兩相非交疊時鐘的控制下,使各流水線子級在采樣和保持狀態之間切換。流水線ADC相鄰兩級的控制時間是相反的,當前一級處于采樣狀態時,后一級處于保持狀態。運放只有在保持狀態時,才能真正被用到,在采樣狀態,運放實際處于重置狀態,輸出是短接的。所以,可以利用流水線ADC的這一特性,使相鄰兩級共用一個運放,從而減小功耗。

評論