如何提高ADC性能 ― 全方位學習模數(shù)轉(zhuǎn)換器(ADC)

ADC性能提高的建議

本文引用地址:http://www.czjhyjcfj.com/article/185532.htm雖然ADC看起來非常簡單,但它們必須正確使用才能獲得最優(yōu)的性能。ADC具有與簡單模擬放大器相同的性能限制,比如有限增益、偏置電壓、共模輸入電壓限制和諧波失真等。ADC的采樣特性需要我們更多地考慮時鐘抖動和混疊。以下一些指南有助于工程師在設計中充分發(fā)揮ADC的全部性能。

模擬輸入

要認真對待ADC的模擬輸入信號,盡量使它保持干凈,“無用輸入”通常會導致“數(shù)字化的無用輸出”。模擬信號路徑應遠離任何快速開關的數(shù)字信號線,以防止噪聲從這些數(shù)字信號線耦合進模擬路徑。

雖然簡化框圖給出的是單端模擬輸入,但在高性能ADC上經(jīng)常使用差分模擬輸入。差分驅(qū)動ADC可以提供更強的共模噪聲抑制性能,由于有更小的片上信號擺幅,因此一般也能獲得更好的交流性能。差分驅(qū)動一般使用差分放大器或變壓器實現(xiàn)。變壓器可以提供比放大器更好的性能,因為有源放大器會帶來影響總體性能的額外噪聲源。但是,如果需要處理的信號含有直流成份,具有隔直流特性的變壓器就不能用。在設計預驅(qū)動電路時必須考慮驅(qū)動放大器的噪聲和線性性能。需要注意的是,因為高性能ADC通常有非常高的輸入帶寬,因此在ADC輸入引腳處直接濾波可以減少混入基帶的寬帶噪聲數(shù)量。

參考輸入

參考輸入應看作是另一個模擬輸入,必須盡可能保持干凈。參考電壓(VREF)上的任何噪聲與模擬信號上的噪聲是沒有區(qū)別的。一般ADC的數(shù)據(jù)手冊上會規(guī)定要求的去耦電容。這些電容應放置在離ADC最近的地方。為了節(jié)省電路板面積,PCB設計師有時會將去耦電容放在PCB的背面,這種情況應盡可能避免,因為過孔的電感會降低高頻時電容的去耦性能。VREF通常用來設置ADC的滿刻度范圍,因此減小VREF電壓值會減小ADC的LSB值,使得ADC對系統(tǒng)噪聲更加敏感(1V滿刻度10位ADC的LSB值等于1V/210=1mV)。

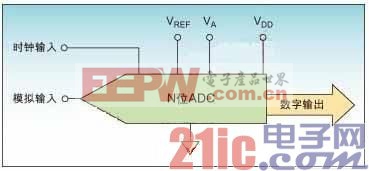

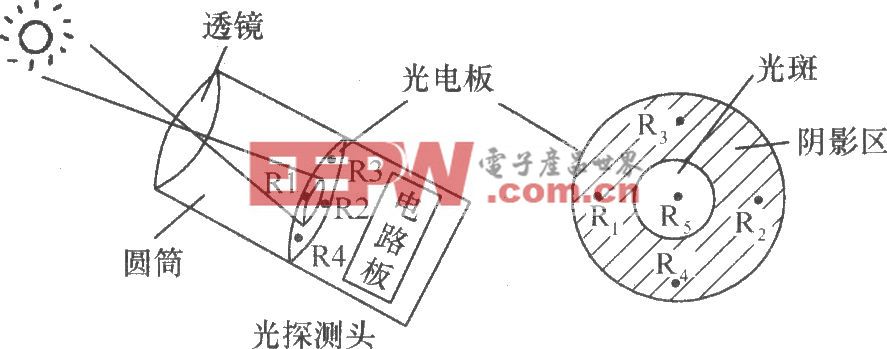

圖1:典型的模數(shù)轉(zhuǎn)換器功能框圖

時鐘輸入

根據(jù)具體的應用,數(shù)字時鐘輸入可能與模擬輸入具有同等的重要性。ADC中有兩大噪聲源:一個是由輸入信號的量化引起的(正比于ADC中的位數(shù)),另一個是由時鐘抖動引起的(在錯誤時間點采樣輸入信號)。根據(jù)以下公式,在非過采樣ADC應用中量化噪聲將限制最大可能的信噪比(SNR)值。

其中,N為ADC的位數(shù)、SNR為信噪比。

從直觀感覺這是有意義的:每增加一位,ADC編碼的總數(shù)量就會增加一倍,量化不確定性可降低一半(6dB)。因此理論上一個10位ADC可以提供61.96dB的SNR。根據(jù)以下等式,采樣時鐘上的任何抖動都會進一步降低SNR:

其中,SNRj是受抖動限制的SNR,fa是模擬輸入頻率,tj是時鐘抖動的均方根(rms)值。

用抖動等于8ps的采樣時鐘數(shù)字化70MHz的模擬信號,可以得到接近49dB SNR的有限抖動,相當于將10位ADC的性能降低到了約8位。時鐘抖動必須小于2ps才能取得等效于10位ADC的SNR。還有許多影響SNR的二階因素,但上述等式是非常好的一階接近函數(shù)。差分時鐘常用來減小抖動。

電源輸入

大多數(shù)ADC有分離的電源輸入,一個用于模擬電路,一個用于數(shù)字電路。推薦在盡量靠近ADC的位置使用足夠多的去耦電容。盡量減少PCB的過孔數(shù)量,并減小從ADC電源引腳到去耦電容的走線長度,從而使ADC和電容之間的電感為最小。就像參考電壓去耦一樣,電路板設計師為了節(jié)省電路板面積有時會把去耦電容放在芯片下方PCB板的背面,基于同樣的理由,這種情況也應避免。ADC數(shù)據(jù)手冊一般會提供推薦的去耦方案。為了達到特定的性能,電源和地經(jīng)常會采用專門的PCB層實現(xiàn)。

數(shù)字輸出

ADC開關數(shù)字信號輸出會產(chǎn)生瞬時噪聲,并向后耦合到ADC中敏感的模擬電路部分,從而引發(fā)故障。縮短輸出走線長度以減小ADC驅(qū)動的電容負載有助于減小這一影響,在ADC輸出端放置串行電阻也可以降低輸出電流尖峰。ADC數(shù)據(jù)手冊通常對此也有一些設計建議。

以上我們介紹了什么是ADC,ADC的技術參數(shù)指標及誤區(qū),并為大家詳述了如何提高ADC性能的一些建議。下面我們將繼續(xù)介紹ADC的一些具體設計中的問題,ADC輸入噪聲利弊分析、ADC輸入轉(zhuǎn)換器電路分析、ADC輸入阻抗信號鏈設計等知識。詳述了ADC的設計挑戰(zhàn),如何從高性能轉(zhuǎn)向低功耗,也對ADC的不同類型數(shù)字輸出進行了深解。

ADC輸入噪聲利弊分析

多數(shù)情況下,輸入噪聲越低越好,但在某些情況下,輸入噪聲實際上有助于實現(xiàn)更高的分辨率。這似乎毫無道理,不過繼續(xù)閱讀本指南,就會明白為什么有些噪聲是好的噪聲。

折合到輸入端噪聲(代碼躍遷噪聲)

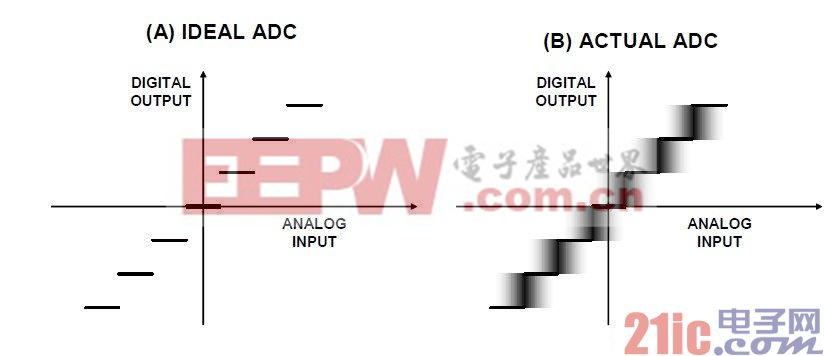

實際的ADC在許多方面與理想的ADC有偏差。折合到輸入端的噪聲肯定不是理想情況下會出現(xiàn)的,它對ADC整體傳遞函數(shù)的影響如圖1所示。隨著模擬輸入電壓提高,理想ADC(如圖1A所示)保持恒定的輸出代碼,直至達到躍遷區(qū),此時輸出代碼即刻跳變?yōu)橄乱粋€值,并且保持該值,直至達到下一個躍遷區(qū)。理論上,理想ADC的代碼躍遷噪聲為0,躍遷區(qū)寬度也等于0.實際的ADC具有一定量的代碼躍遷噪聲,因此躍遷區(qū)寬度取決于折合到輸入端噪聲的量(如圖1B所示)。圖1B顯示的情況是代碼躍遷噪聲的寬度約為1個LSB(最低有效位)峰峰值。

圖1:代碼躍遷噪聲(折合到輸入端噪聲)及其對ADC傳遞函數(shù)的影響

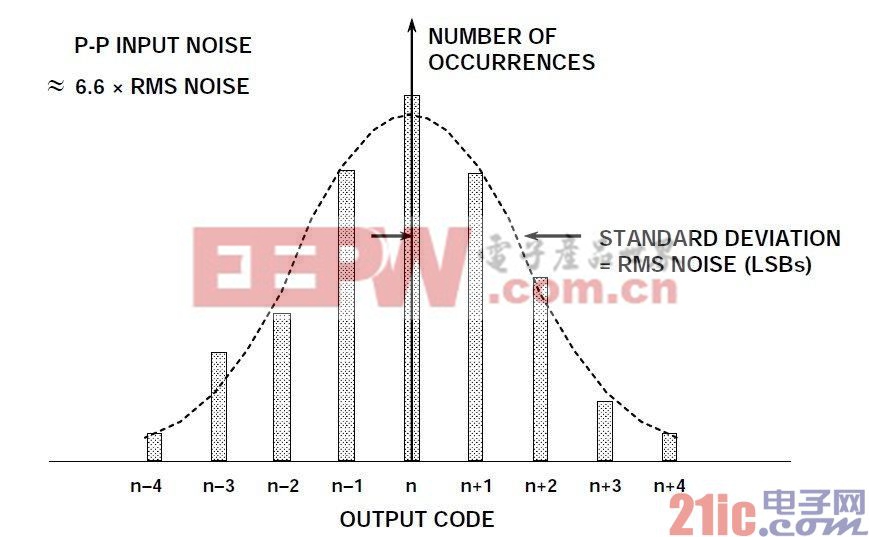

由于電阻噪聲和kT/C噪聲,所有ADC內(nèi)部電路都會產(chǎn)生一定量的均方根(RMS)噪聲。即使是直流輸入信號,此噪聲也存在,它是代碼躍遷噪聲存在的原因。如今通常把代碼躍遷噪聲稱為折合到輸入端噪聲,而不是直接使用代碼躍遷噪聲這一說法。折合到輸入端噪聲通常用ADC輸入為直流值時的若干輸出樣本的直方圖來表征。大多數(shù)高速或高分辨率ADC的輸出為一系列以直流輸入標稱值為中心的代碼(見圖2)。為了測量其值,ADC的輸入端接地或連接到一個深度去耦的電壓源,然后采集大量輸出樣本并將其表示為直方圖(有時也稱為接地輸入直方圖)。由于噪聲大致呈高斯分布,因此可以計算直方圖的標準差σ ,它對應于有效輸入均方根噪聲。參考文獻1詳細說明了如何根據(jù)直方圖數(shù)據(jù)計算σ值。該均方根噪聲雖然可以表示為以ADC滿量程輸入范圍為基準的均方根電壓,但慣例是用LSB rms來表示。

圖2:折合到輸入端噪聲對ADC接地輸入端直方圖的影響(ADC具有少量DNL)

雖然ADC固有的微分非線性(DNL)可能會導致其噪聲分布與理想的高斯分布有細微的偏差(圖2示例中顯示了部分DNL),但它至少大致呈高斯分布。如果DNL比較大,則應計算多個不同直流輸入電壓的 值,然后求平均值。例如,如果代碼分布具有較大且獨特的峰值和谷值,則表明ADC設計不佳,或者更有可能的是PCB布局布線錯誤、接地不良、電源去耦不當(見圖3)。當直流輸入掃過ADC輸入電壓范圍時,如果分布寬度急劇變化,這也表明存在問題。

評論