新開發FinFET整合III-V族與矽材料

比利時微電子研究中心(IMEC)宣稱開發出全球首款在300mm晶圓上整合III-V族與矽晶材料的3DFinFET化合物半導體。IMEC的新制程目標是希望能持續微縮CMOS至7nm及其以下,以及實現混合CMOS-RF與CMOS光電元件的化合物。

本文引用地址:http://www.czjhyjcfj.com/article/185399.htm隨著晶片微縮即將接近原子級的限制,業界致力于提高晶片性能與降低功耗的各種方法逐漸面臨瓶頸。透過為矽晶整合更高性能的材料,例如可提供更高載子速度與更高驅動電流的III-V族電晶體通道,這種新的化合物半導體可望超越矽晶本身性能,持續微縮至更制程。

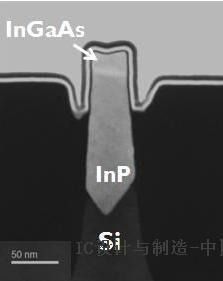

首款在300mm晶圓制造的III-VFinFET電晶體,采用磷化銦(InP))與砷化銦鎵(InGaAs)化合物。

英特爾(Intel)與其他公司已在嘗試結合III-V族材料(如砷化銦鎵與磷化銦)與傳統矽晶基板的化合物半導體了,但一直無法克服材料之間原子晶格難以匹配的挑戰。而今,IMEC聲稱已經成功實現一種晶圓級制程,透過擷取晶體缺陷的長寬比、溝槽結構與外延制程等創新,能夠以砷化銦鎵與磷化銦等材料在3DFinFET上取代矽鰭,同時還能適應8%的晶格不匹配。

「基本上,我們經由FinFET制程至鰭片形成階段,以特定的蝕刻制程從選定的鰭片移除矽晶,蝕刻的圖案能讓III-V族生長以及吸收缺陷,」IMEC邏輯研發總監AaronThean解釋,「我們開始加進III-V族材料,先從磷化銦開始,使其吸收約8%的晶格不匹配,使其最終生長至頂部,然后在凹處再次加進磷化銦,并以砷化銦重新生長至頂部。」

據Thean表示,IMEC的合作夥伴希望這項技術能進一步開發,以期能在2016年到2018間實現7奈米節點的部署。IMEC的CMOS開發合作夥伴將有機會取得該制程,包括英特爾、三星、臺積電、Globalfoundries、美光、海力士、東芝、松下、Sony、高通(Qualcomm)、Altera、富士通、nVidia與Xilinx。

評論