德州儀器新型低相位噪聲時鐘合成器可極大降低成本并縮減能節省 70% 的板級空間

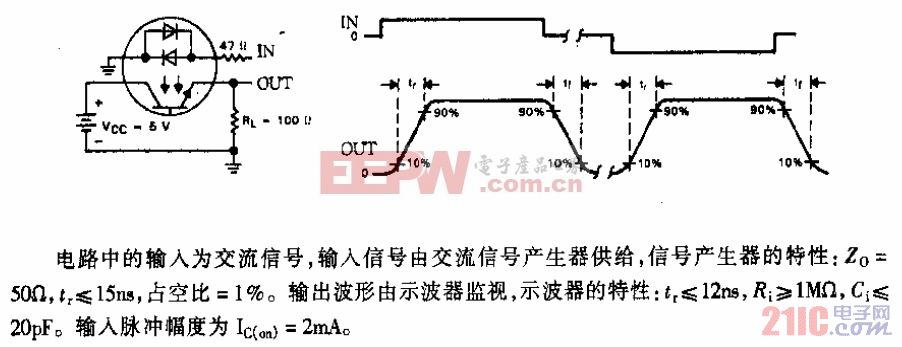

CDC7005完成壓控制晶體振蕩器 (VCXO) 與參考時鐘同步,并集成低噪相位/頻率檢測器、高精度充電泵、可編程除法器、運算放大器以及具有除法選項的 1:5 差分時鐘緩沖器。該器件的低相位噪聲性能非常有益于包括 A/D-D/A 轉換器、串/并轉換器、ASIC 及要求高精度參考定時的數字信號處理器 (DSP) 等在內的眾多眾多信號鏈路器件,是通信、儀表以及工業應用領域的理想選擇。

CDC7005 可接受 3.5 MHz 到 180 MHz 的參考時鐘,并要求 VCXO 時鐘范圍介于 10 MHz~800 MHz 之間以保持同步。通過選擇適當的 VCXO、乘以或除以參考時鐘,以及從單獨可編程除法組合中進行選擇,該器件可輸出高達 180 MHz 的時鐘頻率。

CDC7005 可提供五路低扭曲(Skew)的差動輸出,并可靈活地選擇甚至低于 10 Hz 的最佳 PLL 環路帶寬,從而能夠從進入的參考時鐘清除輸入的參考時鐘中的抖動。集成運算放大器可用于優化具有有源濾波器設計的環路帶寬。此外,在在無需外部組件的情況下也的情況下可編程設置輸出相位。

評論