0.18 μm CMOS帶隙基準電壓源的設計

本文提出了一種基于0.18 μm標準CMOS工藝的高性能帶隙基準電壓源的設計方法,輸出基準電壓0.6 V,輸入電壓范圍為1.5 V~3 V,溫度系數僅為5 ppm/℃,功耗為80 ?滋W.

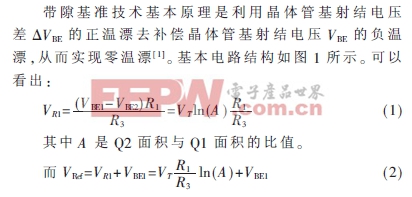

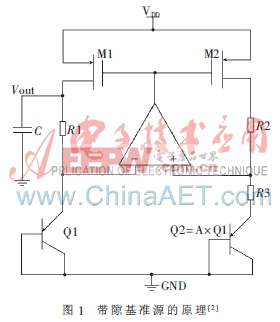

1 帶隙基準技術基本原理

基準電壓源已成為大規模、超大規模集成電路和幾乎所有數字模擬系統中不可缺少的基本電路模塊。基準電壓源可廣泛應用于高精度比較器、A/D和D/A轉換器、隨機動態存儲器、閃存以及系統集成芯片中。帶隙基準電壓源受電源電壓變化的影響很小,它具備了高穩定度、低溫漂、低噪聲的主要優點。

其中,VT具有正溫度系數,VBE1具有負溫度系數,則輸出VRef的溫度系數可以調整到接近零。

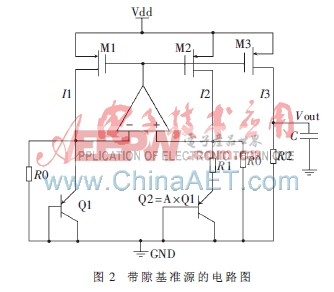

2 帶隙基準源設計電路

為了得到較低的輸出電壓,在兩個晶體管支路上分別并聯一個電阻,根據此原理,設計電路圖[3]如圖2所示。

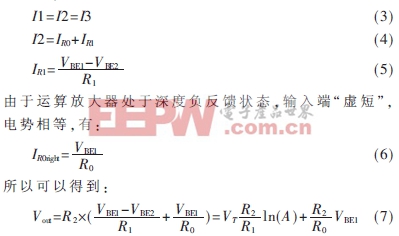

三個PMOS管為同樣寬長的MOS管,均處于飽和工作狀態,根據鏡像原理有:

由式(7)可以看出,調節R2/R1與R2/R0的值,就可以得到零溫度系數的電壓輸出值。雖然電阻本身也具有溫度系數,但在此電路中,輸出電壓只與電阻之間的比值有關,所以電阻的溫度系數對輸出的影響很小。

3 運算放大器的設計

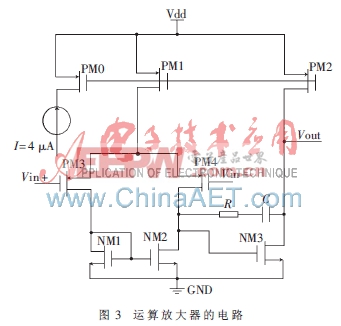

以上推理僅適用于運算放大器工作在理想狀態的情況,圖2電路的最主要部分就是運算放大器,運算效果的優劣決定著此基準電壓源的效果。根據電路的需求,設計的運放有較高的放大倍數、較低的功耗、較低的噪聲,所以選用普通的兩級運放即可,電路圖如圖3所示。

圖3中PM0和PM1作為鏡像電流源,將偏置電流4 μA鏡像給放大器使用,PM3與PM4作為運放的輸入端,比使用NMOS差分對得到更大的輸入范圍,兩級的級聯運放需要加入相位補償電路(圖3電路中串聯的電阻R和電容C支路[4]),仿真后的幅頻響應如圖4所示。

電子鎮流器相關文章:電子鎮流器工作原理

評論