基于FPGA高速實時數據傳輸系統設計方案

.引言

本文引用地址:http://www.czjhyjcfj.com/article/169485.htm信息時代的日新月異,催促著各種各樣的數據信息快馬加鞭,人們在要求信息傳輸得越來越快的同時,還要求信息要來得更加及時,于是高速實時的數據傳輸就成為了電子信息領域里一個永遠不會過時的主題。但是,可以清楚地看到,當今動輒成百上千兆的數據流一股腦的涌入,任何一個高速數據傳輸系統的穩定性和安全性等方方面面的問題都面臨著極大的挑戰,稍有考慮不周之處就會引起各種各樣的問題,因此如何能安全高效的對高速數據進行實時接收、存儲、處理和發送正是此次設計方案的目的。

2.設計方案的硬件選定

鑒于當前高速數據傳輸系統的設計方案大多是現場可編程門陣列(FPGA)加片外存儲介質( SDRAM、SRAM、DDR等)的組合,于是本次設計方案同樣采用這種組合方式,具體為一片 FPGA、三片靜態存儲器( SRAM)和一片高速數據傳輸芯片。 FPGA具有管腳多、內部邏輯資源豐富、足夠的可用 IP核等優點,用作整個高速數據傳輸系統的控制模塊極為合適,此次方案中選用 Altera公司的高性價比 Cyclone[2]系列 FPGA;靜態存儲器具有昀大的優點就是數據讀取速度快,且控制信號簡單易操作,昀適用于高速數據存儲介質,方案選用 ISSI公司的 IS61LV51216型號的靜態存儲器 [3],其處理速度和存儲容量滿足系統設計的需要;TI公司的 TLK1501[4]是此次設計選用的高速數據傳輸芯片,其傳輸能力十分強大,不僅能滿足當前設計的傳輸速度需要,還留有充分的帶寬余量,為以后的系統改進提供了條件。上述三種芯片是此次高速數據傳輸系統所要用到的主要組成部件,其具體連接方式等問題不作討論。

3.具體設計方案

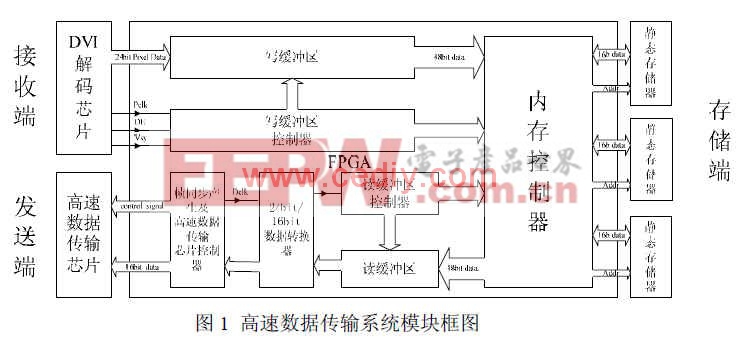

實現整個數據流從接收、存儲、轉換直到發送的過程由圖一可以看出,在接收端經由 DVI[1]解碼芯片傳輸的解碼數據包含 24bit并行像素數據和三個同步信號――像素時鐘 Pclk、數據使能信號 DE以及場同步信號 Vsy,fpga內部的寫緩沖區控制器則會根據以上三個數據同步信號生成寫緩沖區的寫入地址,控制 24bit的像素數據信號存入寫緩沖區中,并會在一段時間后向內存控制器發送讀請求( wcache_rreq)以讀出寫緩沖區內的已寫入數據,寫緩沖區是由 fpga自帶的 M4K塊配置生成的雙端口 RAM結構[2],采用乒乓操作,這樣整個內存讀取和緩沖區寫入過程是各自獨立進行的,保證所寫入數據的完整性,內存控制器在接收寫緩沖區控制器發送的讀請求后,按照相應的寫緩沖區地址讀取數據,并將其寫入片外靜態存儲器中,以上為像素數據的接收和存儲過程;在發送端,幀同步產生及高速數據傳輸控制器通過 fpga自帶的鎖相環產生數據時鐘 Dclk、幀同步 Fsy等信號,使讀緩沖區控制器產生對讀緩沖區的讀取地址,讀緩沖區控制器在產生讀地址的同時,還會在一段時間間隔后向內存控制器發送寫請求( rcache_wreq)以向被讀過的讀緩沖區部分寫入新數據,同樣讀緩沖區也是雙端口 RAM結構,采用乒乓操作,保證被發送數據的連續完整,被讀出的 24bit數據經過一個 24bit/16bit數據轉換器轉換為 16bit并行數據之后才能輸出給高速數據傳輸芯片,而內存控制器在接收讀緩沖區控制器的寫請求后在片外靜態存儲器中讀出相應地址的數據寫入讀緩沖區中,這樣整個數據的接收、存儲、轉換到發送的過程得以實現。

3.1 寫緩沖區控制器的設計

評論