基于Nios的GDM12864A顯示模塊控制

隨著微電子技術的迅猛發展,各種芯片在體積不斷縮小的同時,功能卻越來越強大。FPGA芯片也從最初只有幾千門,發展到數百萬門的規模,I/O口由幾十個發展至上千個。在這種資源極其豐富的情況下,FPGA設計者不再滿足于僅僅用其來設計簡單的應用系統,而開始在一片FPGA上集成一個完整的電子系統,即SOPC(System On Progratomble Chip)。它通常包括片內存儲器和片內微處理器。Altera公司針對其FPGA芯片推出的Nios系列處理器,就是專為SOPC設計而開發的,它是Altera Excalibur嵌入處理器計劃中第一個產品,它成為業界第一款可編程優化的可配置處理器。本文闡述在SOPC中利用Nios處理器實現GDM12864A顯示模塊控制的方法。

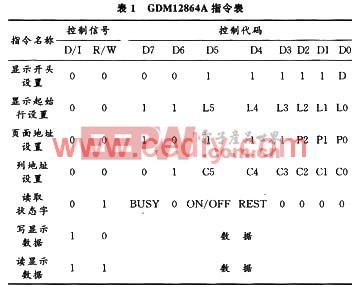

本文引用地址:http://www.czjhyjcfj.com/article/169483.htmGDM12864A是帶顯示存儲器的圖形液晶顯示控制器。它的特點是內置64×64 b的顯示存儲器,顯示屏上各像素點的顯示狀態與顯示存儲器的各位數據一一對應,顯示存儲器的數據直接作為圖形顯示的驅動信號。顯示數據為“1”,相應的像素點顯示;顯示數據為“0”,相應的像素點就不顯示。同時GDM12864A配備了一套顯示存儲器的管理電路和與計算機接口電路,允許計算機直接訪問顯示存儲器。其具體參數如下:64×64 b(512 B)的顯示存儲器,其數據直接作為顯示驅動信號,8位并行數據接口,64路列驅動輸出,低功耗,在顯示期間功耗最大為2 mW,較寬的工作電壓,Vcc=2.7~5.5 V,Vee=0~-10 V。GDM12864A詳細指令如表1所示。

2 Nios軟核

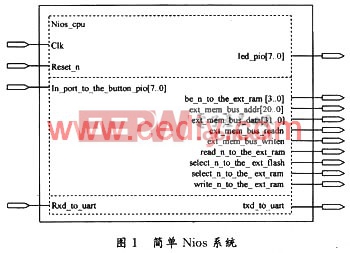

Nios處理器是Altera公司推出的一個具有32/16 b精簡指令集的軟核(Soft Core)CPU,它是面向用戶,可以靈活定制的通用RISC嵌入式處理器,它以軟核的形式交付給用戶,并針對Altera公司的FPGA專門進行了優化。用戶可以在Altera公司提供的開發軟件中加載Nios核和相應的外圍接口并定義相應的指令,然后對設計進行綜合并下載到FPGA中就可以方便地定制一個具有特定功能的嵌入式處理器。用戶可以按照設計的需要選擇添加必要的部件,不會出現資源浪費的現象。圖1即為一個已經設計完成的基本的Nios系統,它包括了一個嵌入式系統工作所需要的所有基本端口,其中有ROM和RAM接口,串口,UART,以及系統的時鐘Clk,另外還有一些外設接口。

3 Nios與顯示模塊的接口電路

利用Nios對GDM12864A進行控制可以有兩種方法:一種方法是將該顯示模塊的接口作為Nios的存儲器或I/O設備直接掛接到Nios的Avalon總線上,Nios以訪問I/O設備或讀寫存儲器的方式對其進行控制。另一種方法是將GDM12864A的接口與Nios的并行端口相連接,Nios通過對其端口的操作來完成對顯示模塊的控制。這種方式具有時序簡單,易實現的優點,可以直接利用軟件完成所有的控制操作。本文將采用第二種控制方式,其接口電路如圖2所示。

圖2中DI為寄存器選擇信號,高電平時選擇數據寄存器,低電平時選擇指令寄存器;RW是讀寫控制信號,RW為高電平時Nios可以從顯示模塊讀取當前狀態,為低電平時Nios向顯示模塊寫數據或指令;E為使能信號。由于GDM12864A是128×64像素的顯示屏,顯示時被分成兩個區域分別顯示,所以在進行控制時需要進行顯示區選擇,也就是片選CS1和CS2。DB[7..0]為并行數據接口,發送指令或讀取狀態都通過對它的操作完成。

評論