基于EPM7128SLC84實現的AD574A采樣控制器

介紹基于Altera公司的EPM7128SLC84芯片實現AD574 A采樣控制器的原理,并給出了相應的VHDL控制程序。

關鍵詞:采樣控制器;VHDL;CPLD

Sample Controller of AD574A Based on EPM7128SLC84

CHEN Bingfei, YANG Bishi

(Nantong Vocational College, Nantong 226007, China)

Key words: sample controller; VHDL; CPLD

1硬件結構

1.1EPM7128SLC84的主要特征

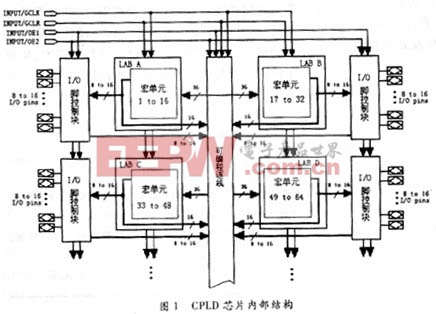

EPM7128SLC84是Altera公司生產的CPLD芯片,該芯片密度為6000門,有60個專用I/O口,PLC C84封裝,正常工作溫度范圍0~70℃。該CPLD芯片內部結構如圖1所示。

1.1EPM7128SLC84的主要特征

EPM7128SLC84是Altera公司生產的CPLD芯片,該芯片密度為6000門,有60個專用I/O口,PLC C84封裝,正常工作溫度范圍0~70℃。該CPLD芯片內部結構如圖1所示。

1.2AD574A主要特征和引腳說明

AD574A是單片高速12位逐次比較型A/D轉換器,內置雙極性電路構成的混合集成轉換芯片;具有外接元件少,功耗低,精度高等特點,并且具有自動校零和自動極性轉換功能。其主要功能特性如下:

分辨率:12位;轉換速率:20μs;電源電壓:±15V和5V;非線性誤差:小于±1/2LSB或± 1LSB:數據輸出格式:12位/8位;模擬電壓輸入范圍:0~10V和0~20V,0~±5V和0~±10V兩檔四種;芯片工作模式:全控工作模式和單一工作模式。

AD574A的管腳示意圖如圖2所示。各引腳功能說明如下:

AD574A是單片高速12位逐次比較型A/D轉換器,內置雙極性電路構成的混合集成轉換芯片;具有外接元件少,功耗低,精度高等特點,并且具有自動校零和自動極性轉換功能。其主要功能特性如下:

分辨率:12位;轉換速率:20μs;電源電壓:±15V和5V;非線性誤差:小于±1/2LSB或± 1LSB:數據輸出格式:12位/8位;模擬電壓輸入范圍:0~10V和0~20V,0~±5V和0~±10V兩檔四種;芯片工作模式:全控工作模式和單一工作模式。

AD574A的管腳示意圖如圖2所示。各引腳功能說明如下:

AD574A的CE、K128、CS、RC和A0對其工作狀態的控制過程如表1所示。

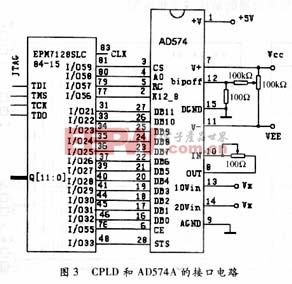

圖3給出的是CPLD和AD574A的接口電路。圖中,標準JTAG接口與PC機并口相連,用于下載設計程序至CPLD中,并可在線編程,方便升級維護。芯片的83引腳接全局時鐘脈沖輸入,Q[11:0]是經過CPLD處理后的穩定數字信號輸出。

由于系統的高速、高可靠性要求,軟件設計部分采用了有限狀態機FSM控制,狀態機控制AD574A的原理如圖4所示。

評論