串行 RapidIO: 高性能嵌入式互連技術(shù)

發(fā)送時(shí),邏輯層和傳輸層將組好的包經(jīng)過CRC編碼后被送到物理層的FIFO中,“8b/10b編碼”模塊將每8bit數(shù)據(jù)編碼成10bits數(shù)據(jù),“并/ 串轉(zhuǎn)換”模塊將10bits并行數(shù)據(jù)轉(zhuǎn)換成串行bits,發(fā)送模塊把數(shù)字bit轉(zhuǎn)換成差分交流耦合信號(hào)在信號(hào)線上發(fā)送出去。這里的8b/10編碼的主要作用是:

1. 保證信號(hào)有足夠的跳變,以便于接收方恢復(fù)時(shí)鐘。串行RapidIO沒有專門的時(shí)鐘信號(hào)線,接收端靠數(shù)據(jù)信號(hào)的跳變恢復(fù)時(shí)鐘。所以需要把信號(hào)跳變少的 8bits數(shù)據(jù)(如全0或全1)編碼成有一定跳變的10bits數(shù)據(jù)。另外,也使得總體數(shù)據(jù)中0和1的個(gè)數(shù)均衡,以消除直流分量,保證交流耦合特性;

2. 8b/10編碼可擴(kuò)大符號(hào)空間,以承載帶內(nèi)控制符號(hào)。10bits能表示1024個(gè)符號(hào),其中256個(gè)表示有效的8bits數(shù)據(jù),剩下的符號(hào)中的幾十個(gè)被用作控制符號(hào)。控制符號(hào)可被用作包分隔符,響應(yīng)標(biāo)志,或用于鏈路初始化,鏈路控制等功能;

3. 8b/10編碼能實(shí)現(xiàn)一定的檢錯(cuò)功能。1024個(gè)符號(hào)中,除了256個(gè)有效數(shù)據(jù)符號(hào)和幾十個(gè)控制符號(hào)外,其它符號(hào)都是非法的,接收方收到非法符號(hào)則表示鏈路傳輸出錯(cuò)。

接收的過程則正好相反,首先接收方需要根據(jù)數(shù)據(jù)信號(hào)的跳變恢復(fù)出時(shí)鐘,用這個(gè)時(shí)鐘采樣串行信號(hào),將串行信號(hào)轉(zhuǎn)換為10bits的并行信號(hào),再按8b/10b編碼規(guī)則解碼得到8bits數(shù)據(jù),最后做CRC校驗(yàn)并送上層處理。

數(shù)據(jù)被正確的接收時(shí),接收端會(huì)發(fā)送一個(gè)ACK響應(yīng)包給發(fā)送端;如果數(shù)據(jù)不正確(CRC錯(cuò)或非法的10bits符號(hào)),則會(huì)送NACK包,要求發(fā)送方重傳。這種重傳糾錯(cuò)的功能由物理層完成,而物理層功能往往由硬件實(shí)現(xiàn),所以不需要軟件干預(yù)。

串行RapidIO支持的信號(hào)速率有三種:1.25GHz,2.5GHz,3.125GHz。但由于8b/10b編碼,其有效數(shù)據(jù)速率分別為:1Gbps, 2Gbps, 2.5Gbps。 4個(gè)1x端口或一個(gè)4x端口支持的最高速率為10Gbps。

串行RapidIO在無(wú)線基礎(chǔ)設(shè)施上的應(yīng)用

無(wú)線基礎(chǔ)設(shè)施如基站、媒體網(wǎng)關(guān)等,是典型的高性能嵌入式通信系統(tǒng),它們對(duì)互連的帶寬、時(shí)延、復(fù)雜度、靈活性、可靠性都有非常高的要求。而串行RapidIO正是滿足這些要求的最佳選擇。

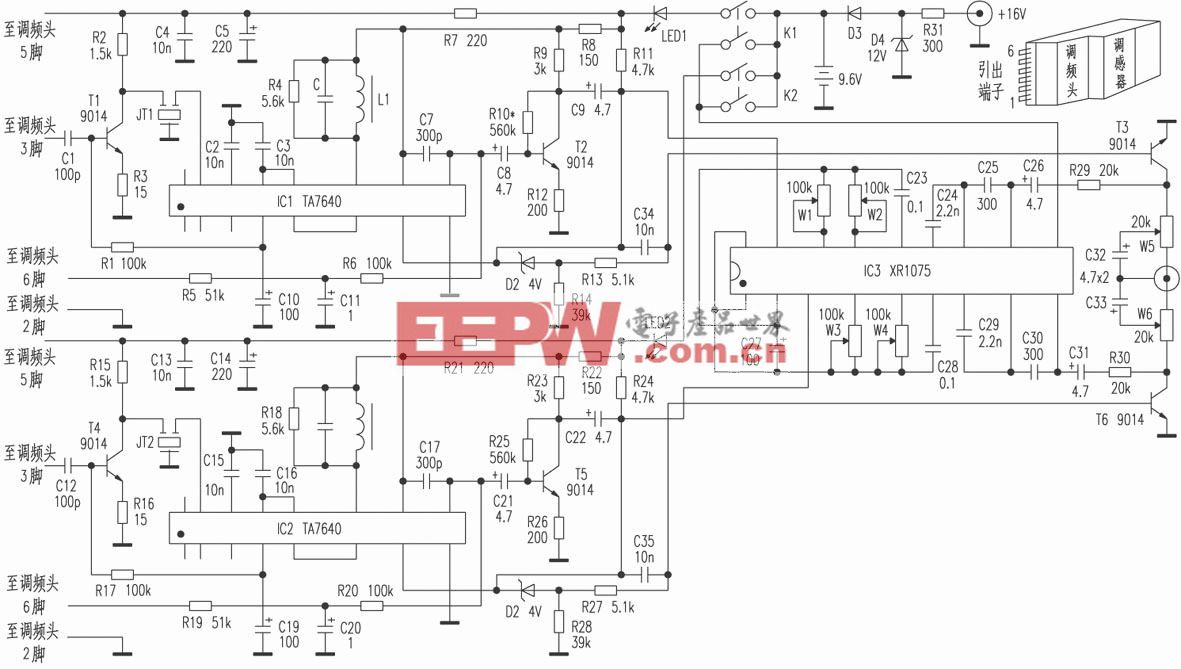

以無(wú)線基站為例,在SRIO出現(xiàn)之前,無(wú)線基站的基帶處理的典型框圖如圖7所示。

圖7 傳統(tǒng)無(wú)線基站基帶處理框圖

在傳統(tǒng)的基站中,DSP與ASIC或FPGA之間的互連一般用外部存儲(chǔ)器接口EMIF(External Memory Interface);DSP之間或DSP與主機(jī)之間一般用HPI(Host Port Interface)或PCI互連。它們的主要缺點(diǎn)是:帶寬小;信號(hào)線多;主從模式接口,不支持對(duì)等傳輸。另外,DSP不能直接進(jìn)行背板傳輸。

使用SRIO(Serial RapidIO)則可有效的解決這些問題,大大提高無(wú)線基站的互連性能。圖8顯示了一種無(wú)線基站基帶互連框圖。在這里,SRIO實(shí)現(xiàn)了大部分器件之間的互連,甚至可支持DSP進(jìn)行直接背板傳輸。

圖8 SRIO提高無(wú)線基站互連性能

通過SRIO交換器件互連可以進(jìn)一步提高基帶處理的靈活性,圖9顯示了一種基帶SRIO交換互連的框圖。這種互連有利于實(shí)現(xiàn)先進(jìn)的基帶處理資源池架構(gòu),數(shù)據(jù)可被送到任何一個(gè)通過SRIO交換器互連的處理器中,從而達(dá)到各個(gè)處理器的負(fù)載均衡,更加有效的利用系統(tǒng)的整體處理能力。

圖9 SRIO交換為無(wú)線基站基帶處理提供更大的靈活性

綜上所述,對(duì)嵌入式系統(tǒng)尤其是無(wú)線基礎(chǔ)設(shè)施,串行RapidIO是最佳的互連技術(shù)。高達(dá)10Gbps的帶寬、低時(shí)延和低軟件復(fù)雜度滿足了飛速發(fā)展的通信技術(shù)對(duì)性能的苛刻需求;串行差分模擬信號(hào)技術(shù)滿足了系統(tǒng)對(duì)管腳數(shù)量的限制,及對(duì)背板傳輸?shù)男枨螅混`活的點(diǎn)對(duì)點(diǎn)對(duì)等互連、交換互連,和可選的 1.25G/2.5G/3.125G三種速度能滿足多種不同應(yīng)用的需求。

隨著串行RapidIO技術(shù)的發(fā)展成熟,以及越來(lái)越多的廠商的支持,串行RapidIO技術(shù)必將成為高性能嵌入式互連的主流技術(shù)。

linux操作系統(tǒng)文章專題:linux操作系統(tǒng)詳解(linux不再難懂)

評(píng)論