SoPC技術在圖像采集和處理系統中的應用設計

1 系統整體方案及硬件設計

系統要求在FPGA片內利用SoPC技術實現便攜式的圖像采集與處理。它通過對原始圖像的掃描,經數字圖像處理與識別后即可將得到的大容量的承載信息(包括文字、頭像、指紋等個人信息)在LCD上顯示,并可通過USB接口將信息拷貝,或通過RS-232接口將信息上傳給PC機,也可以通過GPRS將獲得的信息方便快捷地發往數據中心作驗證。

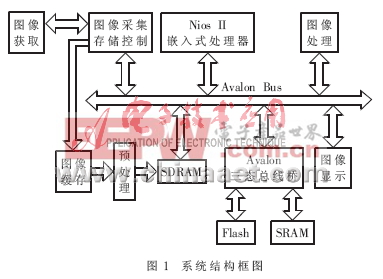

整個系統的核心部分是內嵌Nios II軟核的FPGA,外圍設備和芯片包括圖像獲取設備、顯示器及片外SDRAM和FLASH存儲器、輸入設備等。系統結構框圖如圖1所示。

系統的工作過程是:系統配置完成后,視頻獲取設備獲取視頻圖像,每幀圖像經模數轉換生成圖像數據進入預處理模塊,經預處理后的圖像數據送入SDRAM存儲器,由Nios II處理器進行圖像的后續處理和控制。處理后的圖像經數模轉換在監視器上實時顯示。

1.1 圖像采集接口電路設計

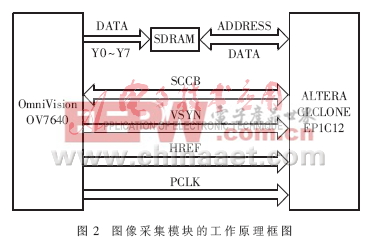

本系統采用美國OmiVision公司的數字式彩色CMOS圖像傳感器OV7640。該芯片分辨率為640×480像素,成像速度為30幀/s,采取逐行掃描方式,輸出為數字信號。工作原理如圖2。

圖像采集的程序流程是:首先Nios初始化OV7640的各個寄存器,主要包括狀態寄存器(STA)、數據和時鐘控制寄存器(CLKRC)、自動增益控制寄存器(AGC)的設置;然后查詢等待,條碼圖像被OV7640采集進入數據寄存器后,通過DMA方式存入SDRAM,Nios再從SDRAM中提取數據進行譯碼。

1.2 基于Nios的SoPC系統硬件設計

基于Nios軟核的SoPC系統設計是整個系統硬件設計的核心,包括Nios軟核處理器的設計、數據采集控制的設計、圖像信號FFT分析的實現、參數顯示以及RS232通信模塊的設計等。另外,使用Nios進行嵌入式設計在硬件上必需使用Altera公司的FPGA。

Nios處理器核的硬件設計是根據系統的功能要求定制合適的CPU和外設,然后在SoPC和Quartus II中實現。在硬件設計流程中,可以靈活定制Nios CPU的許多特性甚至指令,可以使用Altera提供的IP Core來加快設計者開發Nios外設的速度并提高外設性能,也可以使用第三方的IP Core,或者使用VHDL、Verilog自行定制外設。

系統Nios外設主要包括:

(1)CMOS圖像傳感器接口模塊。由于Altera沒有提供CMOS圖像傳感器接口模塊,所以使用VHDL編程自行定制。通過VHDL編程設計一個CMOS圖像傳感器控制模塊,采用接入Avalon總線的方式自定制外設。

(2)由于要對數字圖像信號進行FFT運算,所以采集的數據必須先進行存儲,然后再作FFT計算。因此,必須設計FIFO存儲器和FFT實現的硬件。

(3)RS232通信電路模塊。RS232通信可以通過串行口UART加上一個轉換芯片來實現。所以,本系統利用SoPC中提供的UART組件來實現RS232通信接口的設計。

(4)LCD液晶顯示模塊。LCD液晶顯示是通過配置Nios的PIO接口來控制的。

除上面所述之外,根據系統要求,Nios處理器核應當配置以下組件及接口模塊:cpu、boot_rom(用于系統引導)、uart1(用于系統的仿真調試)、uart_rs232(用于串口通訊)、Timer1(系統內部時鐘)、lan_timer(以太網通信用時鐘)、button_pio(用于參數設置)、lcd_pio(用于參數顯示)、user_logic_ad_nv_ctl和user_logic_ad_power_ctl(自定義的AD轉換的接口模塊)、Ethernet(用于以太網通信)、ext_ram(外部SRAM)、dma(用于將采集的數據直接存入SRAM中)和ext_flash(外部flash)。

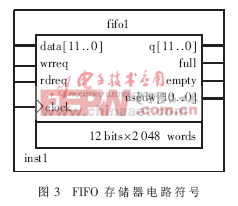

本系統中數據的存儲是通過設計FIFO存儲器電路實現的。FIFO存儲器電路主要由一個雙口RAM模塊(Dual-Port RAM)和狀態機模塊(State Machine Table)組成,通過先進先出(FIFO)堆棧把數據存儲在雙口RAM中。其設計是在Matlab環境下利用Altera DSP Builder設計工具實現的。

電路設計完成并仿真驗證成功后,應用DSP Builder中的signal Compiler進行編譯分析,經signal Compiler轉換后可以變成VHDL語言的程序。同時,在Quartus II中,可以將VHDL語言程序轉換成電路符號,便于應用原理圖的方法設計硬件系統。由FIFO存儲器的VHDL程序生成的電路符號如圖3所示。在設計過程中,需要用到Quartus II軟件和其內嵌的IP Toolbench。按照本系統的要求設置FFT的參數為:點數為1 024點,數據寬度為12 bit。最后設計生成FFT的MegaCore Function模塊,包含一些VHDL程序及其他相關的文件。由VHDL程序生成的FFT模塊電路符號如圖4所示。

電氣符號相關文章:電氣符號大全

存儲器相關文章:存儲器原理

評論