一種新型掃頻儀的設計

摘要 選用了一種基于DSP與FPGA結構的新型射頻掃頻儀的設計方案,重點討論了其掃頻信號源的設計。分析了頻率合成技術的發展趨勢,介紹了PLL技術和DDS技術的原理,并在此基礎上給出了以PLL+DDS方式實現的掃頻信號源設計。

關鍵詞 DSP;掃頻儀;PLL;DDS

頻率特性分析儀即掃頻儀是在示波器基礎上發展起來的一種頻率特性圖示儀,在工程實踐和科學實驗中都有著廣泛的應用,是現代信息產業中一種重要的電子測量儀器。隨著現代電子信息技術的飛速發展,掃頻儀也向著數字化、小型化、智能化的方向發展。DSP、FPGA等技術的應用,解決了傳統掃頻儀體積龐大、操作繁瑣、分立元件多、價格昂貴等問題。

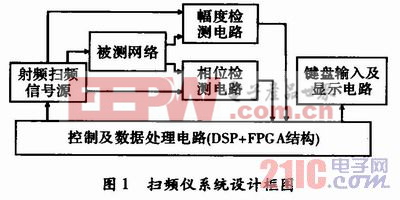

1 掃頻儀系統設計

該系統的設計主要由控制及數據處理電路、掃頻信號源電路、幅度檢測電路、相位檢測電路、鍵盤輸入及顯示電路構成。控制及數據處理電路采用DSP+FPGA的結構設計,DSP具有強大的數據處理能力、較高的運行速度和穩定的性能,而FPGA容量大,靈活性強,能夠進行編程、除錯、再編程和重復操作,可以充分地進行設計開發和驗證。因此由DSP芯片和FPGA可編程邏輯器件所組成的控制及數據處理模塊外圍電路少,運算速度快。

DSP作為主控芯片完成整個系統的控制及采集后的數據處理,FPGA的應用使DSP接口控制簡單容易實現。編寫DSP程序,可以設置頻率起止點和步進,完成頻率掃描。

2 DDS+PLL結構頻率合成法原理

2.1 頻率合成技術

頻率合成是由一個或幾個參考頻率源產生一個或多個頻率的系統元件的組合。隨著技術的進步,尤其是迅速發展的通信領域對于頻率精度和穩定度的要求越來越高,頻率合成技術也受到了越來越多的挑戰。總地來說,頻率合成技術的發展經過了3個階段:(1)直接頻率合成技術;(2)鎖相頻率合成技術(PLL);(3)直接數字頻率合成技術(DDS)。

直接頻率合成由于采用了大量的混頻、分頻、倍頻和濾波,使得頻率合成器體積龐大、成本高、不易調試、指標難以達到需求,已逐漸被模擬或數字鎖相環頻率合成技術代替。

評論