一種新型掃頻儀的設(shè)計(jì)

2.2 數(shù)字PLL技術(shù)

鎖相頻率合成是利用鎖相環(huán)路(PLL)技術(shù)實(shí)現(xiàn)頻率的加、減、乘、除,主要由鑒相器(PD),環(huán)路濾波器(LF)和壓控振蕩器(VCO)組成。鎖相環(huán)原理如圖2所示。本文引用地址:http://www.czjhyjcfj.com/article/150589.htm

PD檢測f1與f2相位差,輸出平均值與該相位差成比例的直流電流。PD產(chǎn)生的脈沖電流經(jīng)過LF產(chǎn)生調(diào)節(jié)電壓,該電壓驅(qū)動(dòng)VCO來增加或減小輸出頻率直到PD平均輸出為零。輸出信號FOUT為

![]()

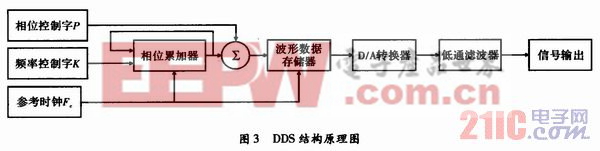

2.3 DDS技術(shù)

DDS技術(shù)從相位的角度出發(fā)直接進(jìn)行頻率合成,能夠?qū)崿F(xiàn)較高的頻率分辨率和較快的頻率轉(zhuǎn)換時(shí)間,典型的DDS由相位累加器、波形存儲器、數(shù)模轉(zhuǎn)換器、低通濾波器和參考時(shí)鐘FC這5部分構(gòu)成。其結(jié)構(gòu)原理框圖如圖3所示。

經(jīng)過對頻率控制字K的線性累加,最終得到其輸出頻率FOUT與時(shí)鐘頻率FC之間的關(guān)系

![]()

其中,N為相位累加器的位數(shù)。

當(dāng)K=1時(shí),得到DDS的頻率分辨率為FC/2N。DDS技術(shù)有多種硬件實(shí)現(xiàn)方式,為了達(dá)到功耗低、集成度高且便于調(diào)試的設(shè)計(jì)目標(biāo),現(xiàn)代頻率合成系統(tǒng)常采用專用的DDS芯片完成設(shè)計(jì)。

2.4 DDS+PLL結(jié)構(gòu)的頻率合成法

由PLL工作機(jī)理可知,當(dāng)輸出頻率和分辨率越高時(shí),倍頻次數(shù)N很大,相位噪聲惡化。而全數(shù)字結(jié)構(gòu)的DDS也有不足:輸出頻率低,輸出譜中雜散多,故難以應(yīng)用于射頻頻率段。適當(dāng)?shù)亟M合PLL和DDS技術(shù)實(shí)現(xiàn)優(yōu)勢互補(bǔ),可以使合成信號兼顧兩者的優(yōu)點(diǎn),DDS+PLL頻率合成主要有3種:(1)DDS激勵(lì)鎖相環(huán);(2)PLL內(nèi)嵌DDS;(3)PLL與DDS環(huán)外混頻。

評論