ARM中斷處理的研究

在嵌入式系統中常用的RISC處理器是ARM核,它具有體積小、功耗低、成本低、性價比高的特點。然而,不管是哪種型號的ARM處理器,也無論該嵌入式系統中是否有操作系統,中斷處理,特別是IRQ中斷,始終是必須的,而中斷處理的核心問題是上下文的保存。能否安全而又高效地保存上下文,將影響一個嵌入式系統的性能與穩定。筆者對ARM處理器的普通中斷處理、任務切換中斷處理、可重人中斷處理和基于優先級的可重人性中斷處理的上下文保存技術進行分析與總結。為保證理論的正確性,核心的程序代碼都經過了實驗的檢測。

本文引用地址:http://www.czjhyjcfj.com/article/150484.htm1 系統中斷處理簡介

ARM處理器的中斷主要有兩種:IRQ普通中斷和FIQ快速中斷。快速中斷本質上與普通中斷沒有太大的差別,它們在處理機制上有許多相同的地方。IRQ中斷是最頻繁的也是最為影響系統性能的,所以對它的研究與處理也就最有價值。

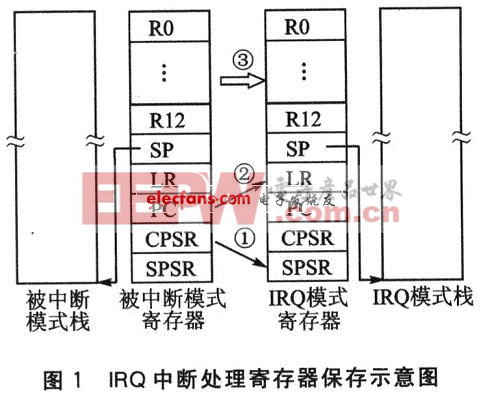

下面簡要地介紹一下IRQ異常發生時ARM處理器的工作過程。在IRQ中斷發生時,ARM處理器的硬件會自動執行以下工作:

①將被中斷任務模式的CPSR值保存到IRQ模式中的SPSR寄存器中;

②將被中斷任務模式的PC值保存到IRQ模式中的LR寄存器中;

③將模式自動切換到IRQ模式,并將CPSR中的bit7位置1禁止后繼IRQ中斷的發生;

④PC被賦予0xl8的地址值,程序將從0xl8片開始執行。結合圖1,可以更好地理解ARM中斷處理機制的工作過程。

2 普通中斷處理

有些ARM嵌入式系統可能對中斷的要求比較低,即發生中斷后首先查詢相應的中斷源,然后進行中斷服務,最后從中斷服務程序中返回到被中斷處繼續運行程序。如何在這種簡單應用中保證安全又高效地處理中斷呢?“安全”就意味著中斷發生時上下文被完好保存不被破壞,“高效”就是說保存盡可能少的寄存器(當然是建立在安全的基礎上的)。由圖1可知,在普通中斷處理中,中斷服務就可以在IRQ模式中運行。根據ATPCS的調用規則,在子程序調用中ARM編譯器保存了R4~R11寄存器,因此就沒有必要再次保存。那么剩下的寄存器就必須予以保存,防止從中斷服務程序返回后被破壞。可以用匯編語言和C語言書寫處理代碼。

首先假設初始化代碼中已正確建立了IRQ堆棧。

所有已使能中斷的查詢與服務>

;將同時發生的中斷全部服務,以提高效率

LDMFD SP!,{R0-R3,R12,R14} ;恢復上下文

在上述保存上下文中沒有必要保存SPSR。因在非嵌套的中斷處理程序中,它不會被任何順序的中斷所破壞。

如果用C語言來書寫該處理程序,可以使用關鍵字一IRQ來說明,以告訴編譯器實現如下的操作:

①保存.ATPCS規定的被破壞的寄存器;

②保存其他中斷處理程序中用到的寄存器;

③同時將(LR-4)賦予程序計數器PC,實現中斷程序的返回并且恢復CPSR寄存器的內容。

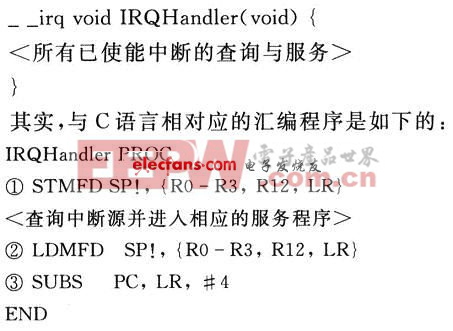

普通中斷處理的C語言程序可以按如下格式編寫:

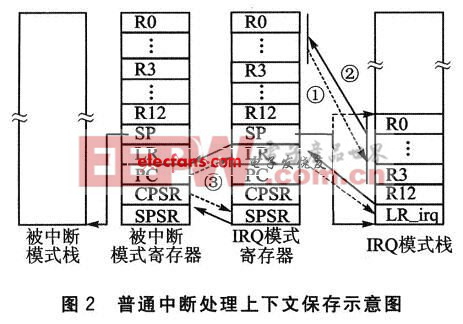

可見,無論是用C語言還是匯編語言來編寫,它們的工作原理都是一樣的。圖2給出了普通中斷處理過程中,ARM寄存器的保存示意圖(虛線是壓棧保存,實線是彈棧恢復)。圖中與程序處理的步驟相對應,可以幫助理解處理器上下文的保存過程。

評論