基于ADV7125的嵌入式系統VGA接口設計

摘要:主要闡述了基于ADV7125芯片的嵌入式系統的VGA接口設計方案。利用S3C2440處理器自帶的LCD控制器來構造VGA時序,然后配合相應的控制信號,通過ADV7125硬件電路把S3C2440輸出的LCD信號轉換為標準的VGA信號輸出。實驗表明,該轉換接口電路簡單、可靠。

關鍵詞:S3C2440;嵌入式系統;ADV7125;VGA接口

引言

目前VGA接口是計算機系統以及智能儀器中重要的標準輸出接口,但是大部分硬件系統選擇LCD終端輸出。很多顯示設備,如常見的CRT或LCD顯示器一般都采用統一的15針VGA顯示接口。如需要外接這些設備,則需要把LCD輸出信號的接口轉換為VGA接口。本設計是在三星公司芯片S3C2440平臺下,利用最高頻率可以達到330 MHz的ADV7125芯片,設計了能夠把輸出的LCD信號轉換為VGA信號的轉換電路。該設計方案具有電路簡單、價格低廉、輸出圖像清晰穩定等特點。

1 ADV7125芯片介紹

ADV7125是一款單芯片、3通道、高速度的數模轉換器。內置3個高速、8位、帶互補輸出的視頻DAC、1個標準TTL輸入接口,以及1個高阻抗、模擬輸出電流源。它具有3個獨立的8位寬輸入端口。只需1個+5 V/+3.3V單電源和時鐘便能工作。ADV7125還具有其他視頻控制信號:復合同步信號控制端![]() 、消隱信號控制端

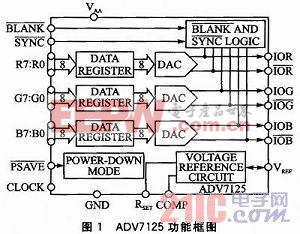

、消隱信號控制端![]() ,以及省電模式控制端。它能夠與各種高分辨率彩色圖形系統兼容。ADV7125功能框圖如圖1所示。

,以及省電模式控制端。它能夠與各種高分辨率彩色圖形系統兼容。ADV7125功能框圖如圖1所示。

ADV7125有3個視頻數據寄存器DATA REGISTER和一個視頻控制寄存器POWER-DOWN MODE。數據寄存器的3個輸入端分別連接紅綠藍三色的數字視頻信號,數據寄存器后面緊跟數模轉換單元,將數字信號轉換為模擬信號;控制寄存器將數字的消隱信號、同步信號轉換合并。數模轉換后的模擬視頻信號和控制寄存器輸出的同步、消隱控制信號共同作為ADV7125的輸出信號,此輸出信號大小受Rset端和地之間接入的外加電阻RSET大小的控制。

2 ADV7125芯片用于VGA轉換的基本原理

ADV7125芯片用于VGA轉換的基本原理是,將S3C2440輸出的數字視頻信號轉換為模擬的VGA輸出信號,模擬的VGA輸出信號的大小受ADV71 25芯片外圍參考電壓VREF和外加電阻RSET的控制,(VREF和RSET的具體接法如圖4所示)其關系如下:

![]()

式中IOG、IOR、IOB分別代表綠、紅、藍三色信號的幅度。當不用復合同步信號![]() 時,需要把

時,需要把![]() 端連接低電平,這時IOG的關系式同式(2)。

端連接低電平,這時IOG的關系式同式(2)。

上式中的![]() 是ADV7125的一個附加信號控制端,ADV7125的另外一個附加信號控制端是

是ADV7125的一個附加信號控制端,ADV7125的另外一個附加信號控制端是![]() (消隱信號控制端)。

(消隱信號控制端)。![]() 和

和![]() 都是在時鐘上升沿被鎖存,保證像素數據流的同步。

都是在時鐘上升沿被鎖存,保證像素數據流的同步。![]() 和

和![]() 的功能是:通過視頻同步信號的編碼,影響VGA視頻信號的輸出。通過在模擬輸出端口內部加了一個加權電流,實現此功能。這個電流的有無,由

的功能是:通過視頻同步信號的編碼,影響VGA視頻信號的輸出。通過在模擬輸出端口內部加了一個加權電流,實現此功能。這個電流的有無,由![]() 和

和![]() 邏輯輸入判定。

邏輯輸入判定。

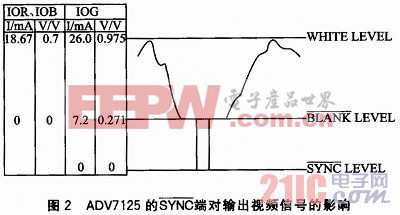

圖2說明了當![]() 和

和![]() 兩者都為高電平時,IOR和IOB兩者與IOG的對比。

兩者都為高電平時,IOR和IOB兩者與IOG的對比。

表1詳細說明了![]() 和

和![]() 對模擬輸出的影響。該表是在VREF=1.235 V,RSET=530 Ω,RLOAD=37.5Ω的條件下測量的。

對模擬輸出的影響。該表是在VREF=1.235 V,RSET=530 Ω,RLOAD=37.5Ω的條件下測量的。

評論