雙掃描使能低功率觸發設計 限制SoC的移位模式中的功耗

所有的SoC使用掃描鏈來檢測設計中是否存在任何制造缺陷。掃描鏈是專為測試而設計的,以串聯方式按順序連接芯片的時序單元。隨著越來越多的功能被集成在SoC中,SoC中的觸發器(時序單元)和組合邏輯的總數量不斷增加。在掃描移位階段,峰值功率是一個大問題,因為在完整的移進移出階段,所有的觸發器隨著組合邏輯的切換而觸發,而如果峰值功率超過允許的極限,移位數據可能會被破壞,這樣由于偽故障而影響芯片的成品率。本文介紹了一個觸發設計,可以對移位過程中的組合邏輯切換進行門控,從而保證設計的峰值功率和平均動態功率。

本文引用地址:http://www.czjhyjcfj.com/article/142399.htm問題描述:設計中使用的測試掃描鏈連接設計的所有時序單元

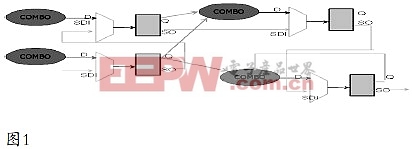

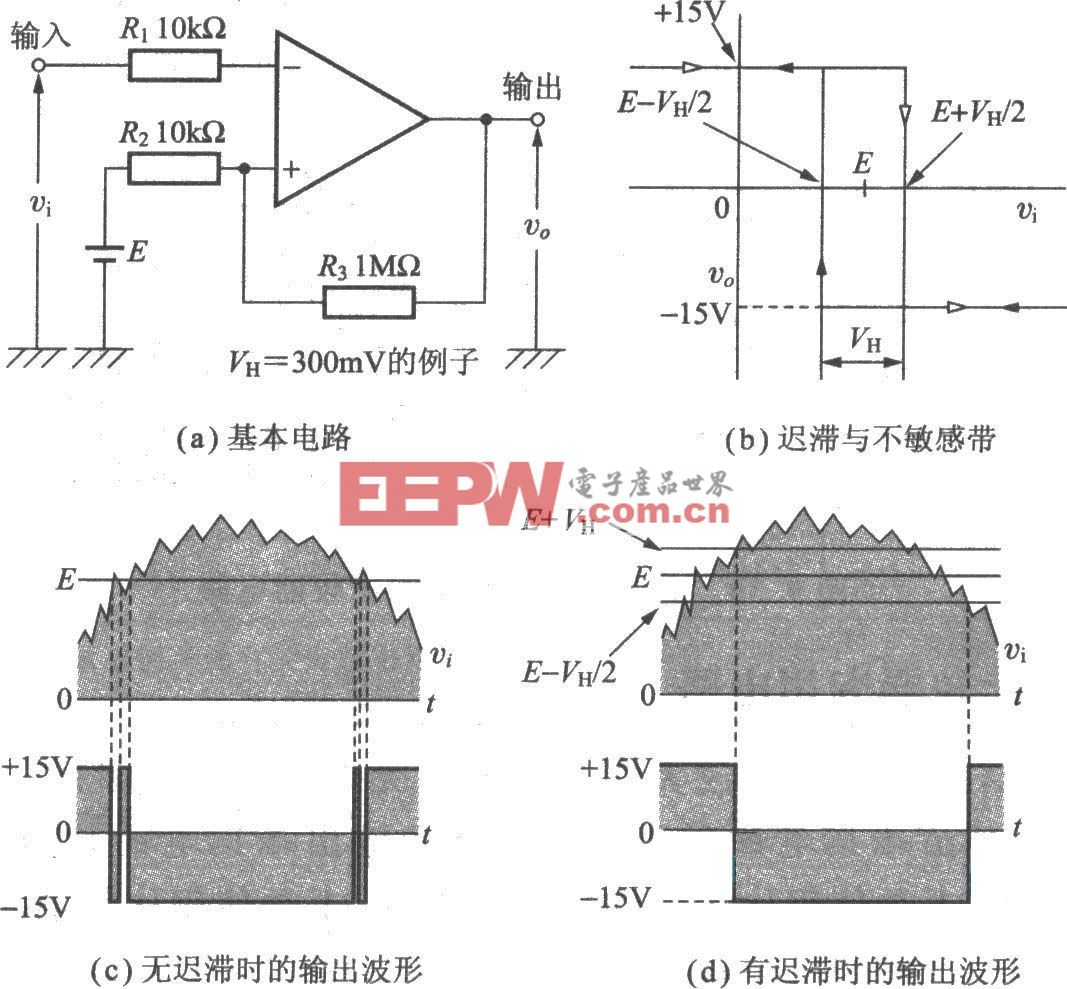

在多個鏈中,一個典型的觸發器具有兩個輸出,功能輸出(Q)和掃描輸出(SO),在內部它們彼此短接在一起。觸發器設計師提供了專門的掃描輸出,可以在移位中輕松收斂保持定時。當SoC處于移位模式時,觸發器的掃描輸出直接連接到掃描鏈中下一個觸發器的掃描輸入,由于沒有任何組合邏輯,這對保持定時來說是非常嚴峻的問題。因此,為了避免這個問題,設計師提供了專用的掃描輸出,這是延遲版的功能輸出(Q)。這樣,在移進和移出階段,功能輸出Q與掃描輸出SO一起繼續根據掃描輸入SI進行切換。由于功能輸出Q切換,整個功能組合邏輯也在完整的移進移出階段繼續切換。圖1顯示了上述概念。

解決這個問題的動機

限制移位過程中的功率非常重要。挑戰在于不影響設計的情況下,限制實例數和測試時間。目前,有幾種方式來實現這一目標,如減少移頻,建立多個移位域,然后按順序運行它們,限制移位模式產生過程中的切換等。但所有這些解決方案會影響測試時間,從而增加測試成本。

因此,通過停止不必要的組合邏輯切換,可以顯著減少移位過程中的峰值功耗。

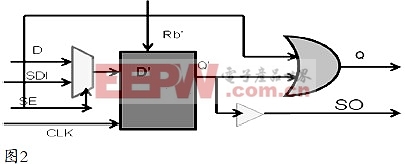

其中一種實現方式是對移位過程中的功能輸出進行門控,然后在捕獲周期中取消門控。之前在這方面已經有一些工作已經完成,而且已經有現成的技術(美國7650548 B2),通過掃描功能對功能輸出進行門控。所以,思路很簡單,因為在移位過程中掃描使能設置為1,功能輸出將保持不變,在捕獲周期時則取消門控,這樣捕獲到的就是最新掃描輸入的值,而不是一些舊的或恒定值。見圖2。

評論