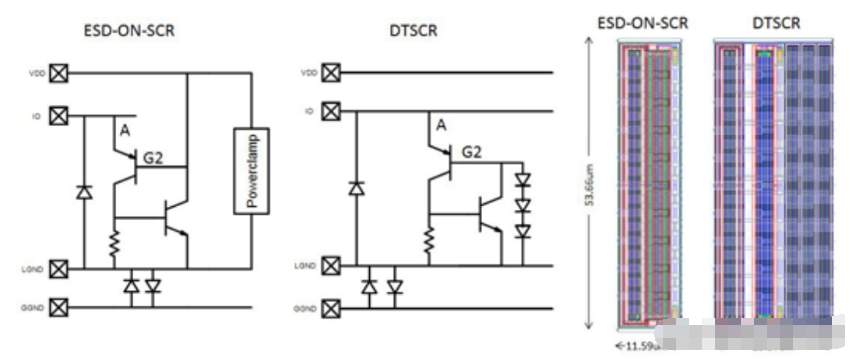

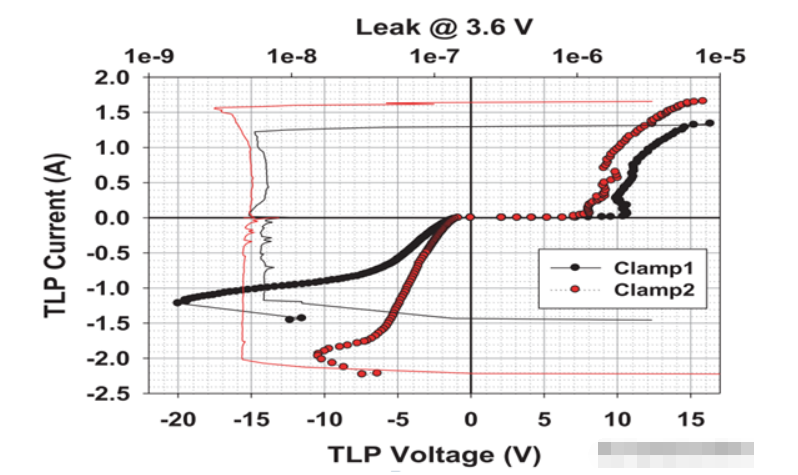

-通過電壓/電流曲線分析,深入了解靜電放電防護組件(ESD Protection Device)之物理特性。

-在芯片制作完成之初,即能先預測產品之靜電放電的承受能力,以增加產品的研發效率。

-重視HBM ESD pulse所造成的IC失效模式及電性行為。

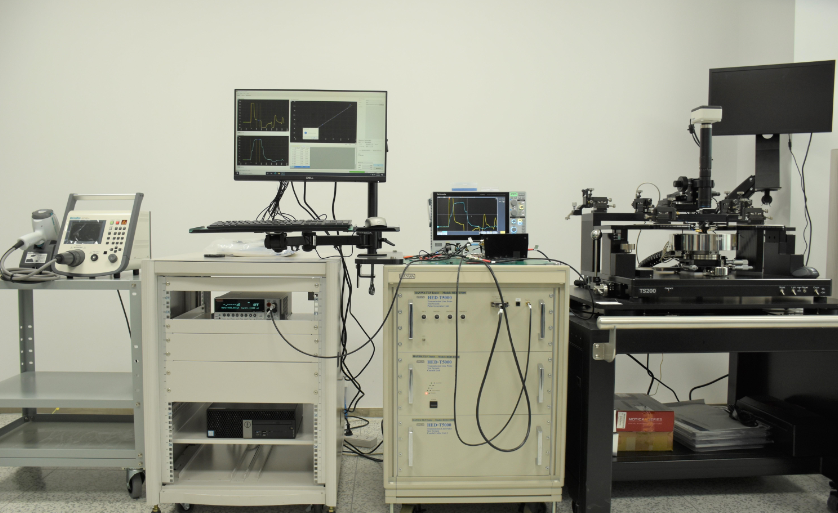

Nomal TLP

TLP test model | TDR(Time Domain Reflection) |

Pulse Voltage | Max:+/-2000V(0.1V/step) |

Pulse Current | Max.40A |

Pulse Width | 100ns |

Pulse rise time | 200ps/2ns/10ns/20ns/50ns |

VF TLP

TLP test model | TDR(Time Domain Reflection) |

Pulse Voltage | Terminal Open: +/-1000V(0.1V/step) 50Ω load:+/-500V(0.2V/step) |

Pulse Current | Short:Max.20A, 50Ω load:Max. 10A |

Pulse Width | 1ns/2ns/3ns |

Pulse rise time | 200ps/2ns/10ns/20ns/50ns |

TLP測試系統

電性栓鎖測試用來評價CMOS ICs對噪聲或者瞬時的免疫程度 (Immunity of transient induced due to external noise or internal under/over-shoot)。栓鎖效應是一種在CMOS、Bipolar或BiCMOS里p-n-p-n 4 層SCR架構的寄生電路(Parasitic circuit)n所造成的影響。

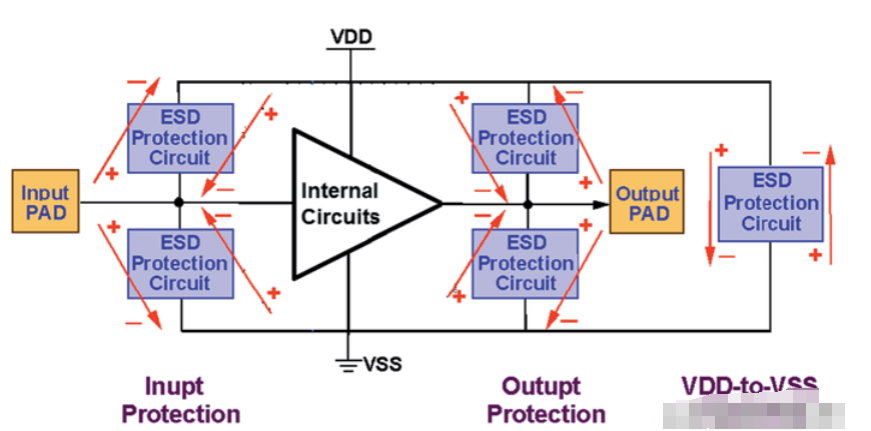

ESD/Latch-up保護電路設計ESD /電性栓鎖測試服務之外,平臺同時提供ESD I/O庫、ESD/電性栓鎖電路設計咨詢、以及客戶電路布局的詳細分析,由此協助客戶的芯片或產品達到最佳的ESD/電性栓鎖防護能力。