lvds 文章 最新資訊

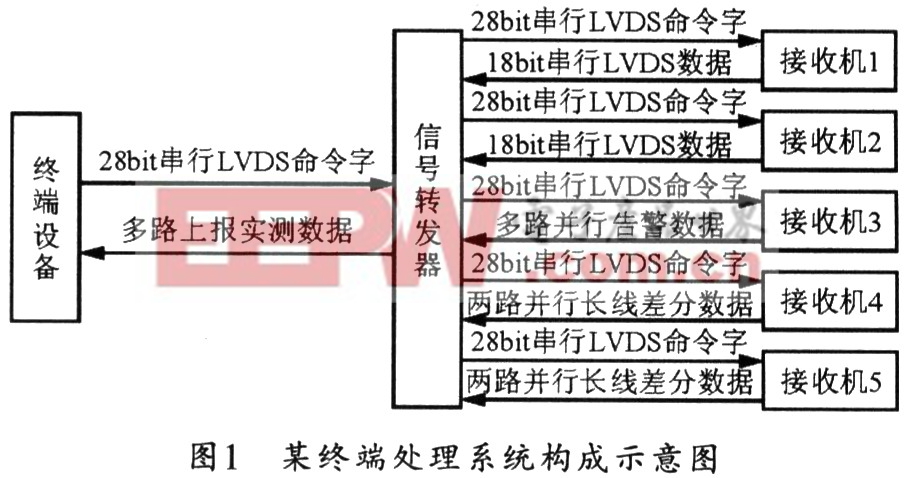

多路串行LVDS信號轉(zhuǎn)發(fā)電路 的設(shè)計與實現(xiàn)

- O 引言

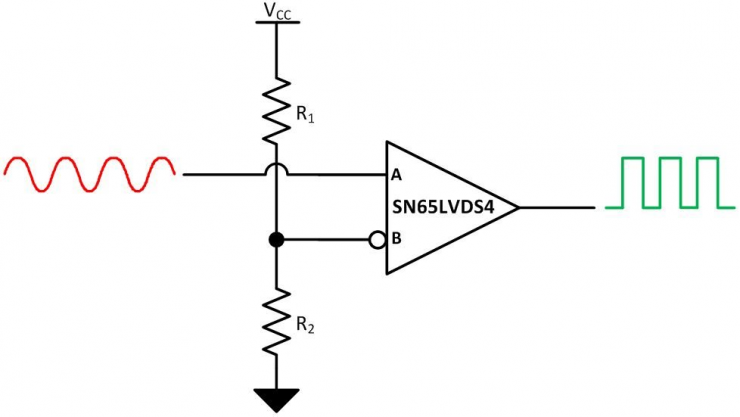

現(xiàn)代雷達和通訊系統(tǒng)中的電磁環(huán)境越來越復雜。為了保證系統(tǒng)控制命令的準確下發(fā),提高控制信號的抗干擾能力,并兼顧降低系統(tǒng)功耗,可采用串行LVDS信號格式來設(shè)計轉(zhuǎn)發(fā)電路。

1 終端處理系統(tǒng)的構(gòu)成

某 - 關(guān)鍵字: 設(shè)計 實現(xiàn) 電路 轉(zhuǎn)發(fā) LVDS 信號 串行 多路串行 LVDS 信號轉(zhuǎn)發(fā) 差分阻抗匹配 電磁兼容 SN65LVDS108

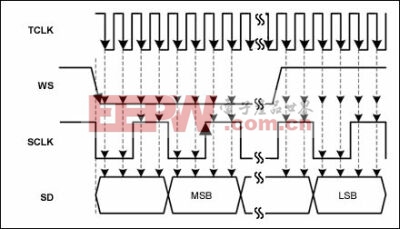

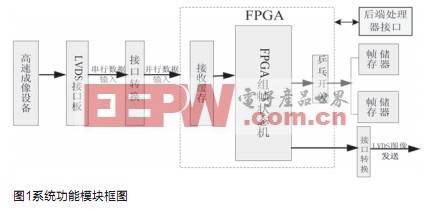

基于FPGA的遠程圖像采集系統(tǒng)設(shè)計

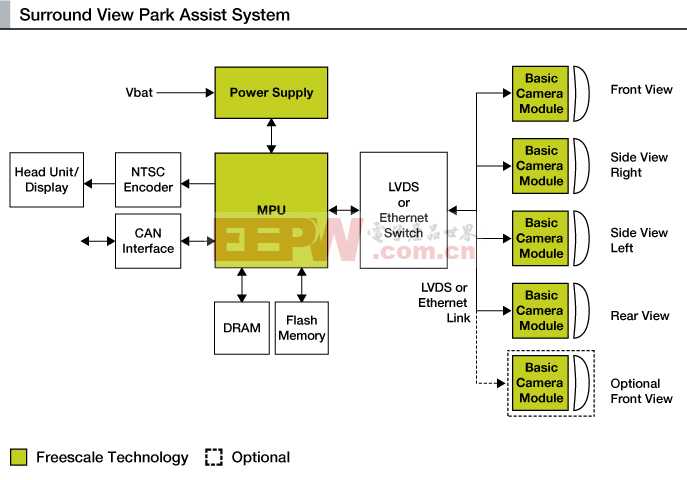

- 本文介紹了一種基于FPGA實現(xiàn)的圖像采集系統(tǒng),通過FPGA控制外部高速成像設(shè)備所產(chǎn)生的圖像數(shù)據(jù)、參數(shù)信息和狀態(tài)控制信號的同步采集,并實現(xiàn)數(shù)據(jù)格式的轉(zhuǎn)換、圖像數(shù)據(jù)的組幀、存儲及轉(zhuǎn)發(fā)功能。

- 關(guān)鍵字: FPGA 圖像采集 組幀狀態(tài)機 LVDS 200911

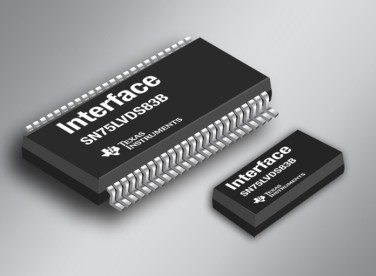

TI 推出可直接與供電處理器連接的 LVDS 串行器

- 日前,德州儀器 (TI) 宣布推出首款可直接與 1.8V 供電處理器連接的 LVDS 串行器。SN75LVDS83B 采用 TI FlatLink 技術(shù),無需使用 1.8V 及 2.5V 邏輯接口所需的高成本電平轉(zhuǎn)換器,從而不僅可顯著降低成本,而且還可將板級空間縮減達 83%。SN75LVDS83B 支持 8 位色彩,并可串行化 RGB 數(shù)據(jù)。此外,該器件還在一個 LVDS 時鐘以及 4 個 LVDS 數(shù)據(jù)對 (data pair) 中高度整合了 24 條數(shù)據(jù)線,從而實現(xiàn)了與 LCD 模塊的連接。

- 關(guān)鍵字: TI FlatLink LVDS 串行器 SN75LVDS83B

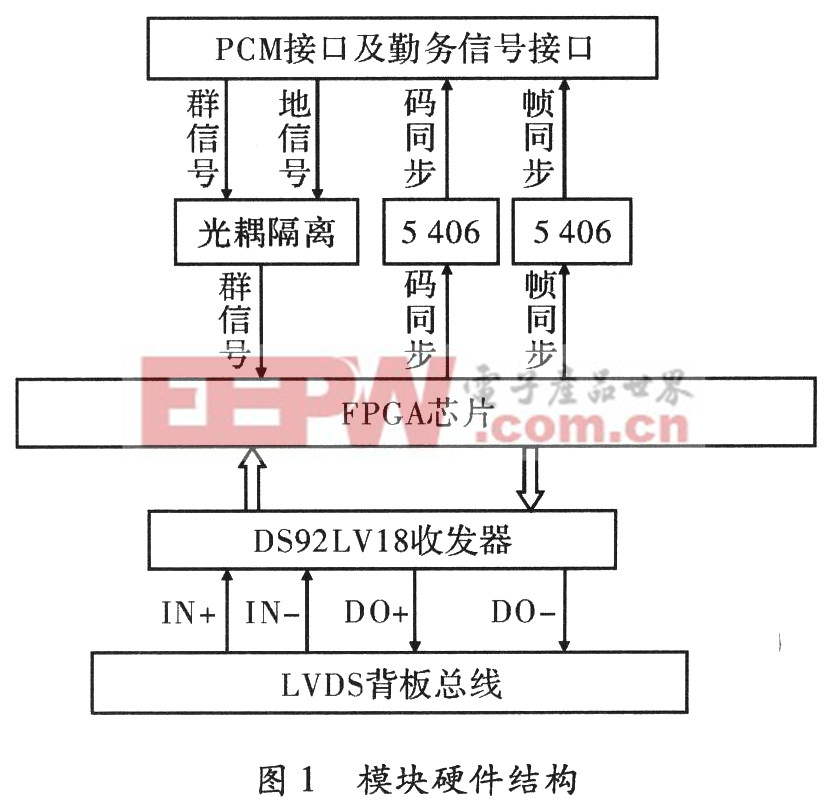

基于FPGA的LVDS高速差分板間接口應(yīng)用

- 隨著ADC器件速率的提高以及FPGA、DSP器件運算速度的提升,高速AD和信號處理系統(tǒng)之間需要進行高速、穩(wěn)定的數(shù)據(jù)傳輸,原來廣泛應(yīng)用CPCI以及FDPD高速總線的帶寬已經(jīng)無法滿足寬帶接收機的數(shù)據(jù)傳輸速率要求,成為影響接收機性能的新瓶頸。針對這一情況,提出了一種基于LVDS差分接口的DDR傳輸接口,解決了這一瓶頸,并且在實際硬件平臺上進行了FPGA實現(xiàn),達到了18.4 Gbit/s的接口速率。

- 關(guān)鍵字: FPGA LVDS 差分板 接口應(yīng)用

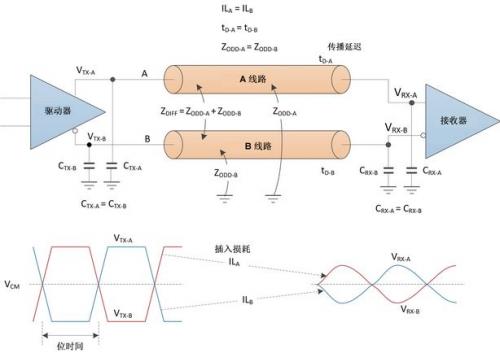

基于LVDS總線的高速長距數(shù)據(jù)傳輸?shù)脑O(shè)計

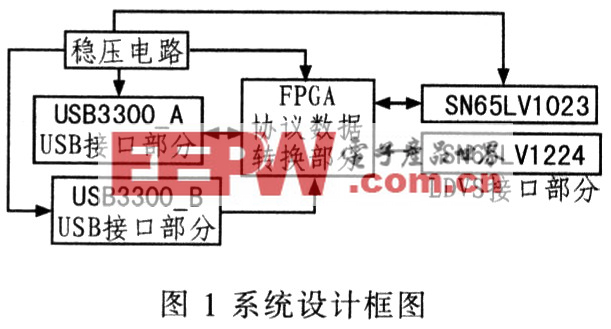

- 采用無信號調(diào)節(jié)功能的低電壓差分信號LVDS(Low―Voltage Differentical Signaling)器件接入通信設(shè)備,其電纜長度一般為幾米;但采用具有驅(qū)動器預(yù)加重功能和接收器均衡功能的LVDS器件,其電纜長度可達數(shù)百米。采用LVDS

接口器件的系統(tǒng)如果需長距離傳輸數(shù)據(jù),可采用電纜驅(qū)動器。該系統(tǒng)采用DS92LVl023和DS92LVl224型的LVDS器件與驅(qū)動器件CLC006和CLC014相配合,可實現(xiàn)傳輸300米的距離。該系統(tǒng)設(shè)計已投入使用,其性能可靠工作穩(wěn)定。 - 關(guān)鍵字: LVDS 總線 數(shù)據(jù)傳輸

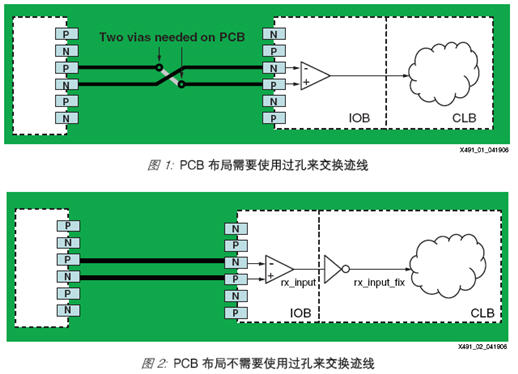

Spartan-3 FPGA系列中高效PCB布局的LVDS信號倒相

- 提要 在比較簡單的未大量使用過孔的四層或六層 PCB 上,可能很難對 LVDS 或 LVPECL 這類差分信號布線。其原因是,驅(qū)動器上的正極引腳必須驅(qū)動接收器上的相應(yīng)正極引腳,而負極引腳則必須驅(qū)動接收器的負極引腳。有時跡線以錯誤的方向結(jié)束,這實際上是向電路中添加了一個倒相器。本應(yīng)用指南說明 Spartan?- 3 FPGA 系列如何僅通過在接收器數(shù)據(jù)通路中加入一個倒相器即可避免大量使用過孔,并且在不要求 PCB 重新設(shè)計的情況下即可解決意外的 PCB 跡線交換問題。這項技術(shù)同樣適用于將 FPGA

- 關(guān)鍵字: PCB LVDS 倒相器 FPGA SDR

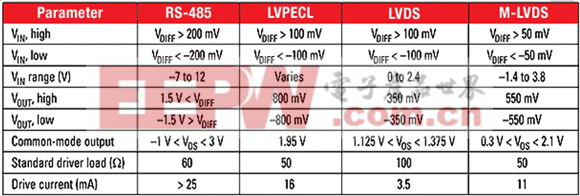

lvds介紹

Low-Voltage Differential Signaling 低壓差分信號

1994年由美國國家半導體公司提出的一種信號傳輸模式,它是一種標準

它在提供高數(shù)據(jù)傳輸率的同時會有很低的功耗,另外它還有許多其他的優(yōu)勢:

1、低電壓電源的兼容性

2、低噪聲

3、高噪聲抑制能力

4、可靠的信號傳輸

5、能夠集成到系統(tǒng)級IC內(nèi)

使用LVDS技術(shù)的的產(chǎn)品數(shù) [ 查看詳細 ]

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司