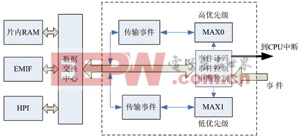

基于 DSP-dMAX 的嵌入式 FIFO 數據傳輸系統設計,本文介紹了基于C6727B的dMAX的基本結構以及基于dMAX的嵌入式FIFO軟硬件設計,設置通用GPIO引腳作為中斷,為了加快FIFO的傳輸速率,使用突發讀寫方式進行數據傳輸。嵌入式FIFO的實現,使得DSP和外部設備的通信更加方便和快捷,而且不需要CPU的參與,減輕了CPU的負擔,CPU可以專注于復雜的算法處理。

關鍵字:

傳輸系統 設計 數據 FIFO DSP-dMAX 嵌入式 基于

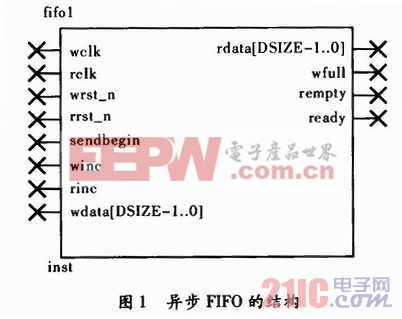

摘要 利用異步FIFO實現FPGA與DSP進行數據通信的方案。FPGA在寫時鐘的控制下將數據寫入FIFO,再與DSP進行握手后,DSP通過EMIFA接口將數據讀入。文中給出了異步FIFO的實現代碼和FPGA與DSP的硬件連接電路。經驗證,利用

關鍵字:

通信 運用 DSP FPGA FIFO 異步

摘要:以Altera公司的FPGA芯片EP2C20Q208C8為例,詳細介紹了在QuartusII 7.2的環境下,用SOPC Builder構建Nios軟核時,自定義FIFO接口元件的方法。通過將采集到的電壓信號,在數碼管上顯示的實驗,實現FIFO寄存器與

關鍵字:

SOPC FIFO 自定義 外設

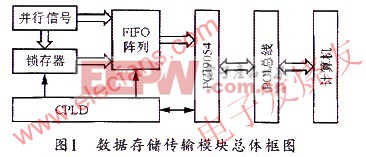

聲發射技術是光纖傳感技術和聲發射技術相結合的產物,是目前聲發射技術的發展趨勢。它將高靈敏度聲發射傳感器安裝于受力構件表面以形成一定數目的傳感器陣列,實時接收和采集來自于材料缺陷的聲發射信號,進而通

關鍵字:

數據傳輸 存儲 信號 發射 fifo 存儲器 基于

1 FIFO概述

關鍵字:

V3680 FIFO 3680 72V

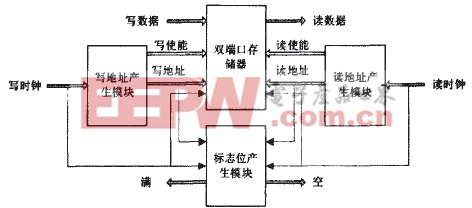

FIFO芯片IDT72V3680的功能特點及應用,1 FIFO概述 FIFO芯片是一種具有存儲功能的高速邏輯芯片,可在高速數字系統中用作數據緩存。FIFO通常利用雙口RAM和讀寫地址產生模塊來實現其功能。FIFO的接口信號包括異步寫時鐘(wr-clk)和讀時鐘(rd-clk)、與

關鍵字:

特點 應用 功能 IDT72V3680 芯片 FIFO

在高頻超聲波數據采集系統中,很多高速A/D轉換器往往不能直接與處理器相連接,這時就需要使用FIFO在處理器...

關鍵字:

FIFO 超聲測厚 ARM

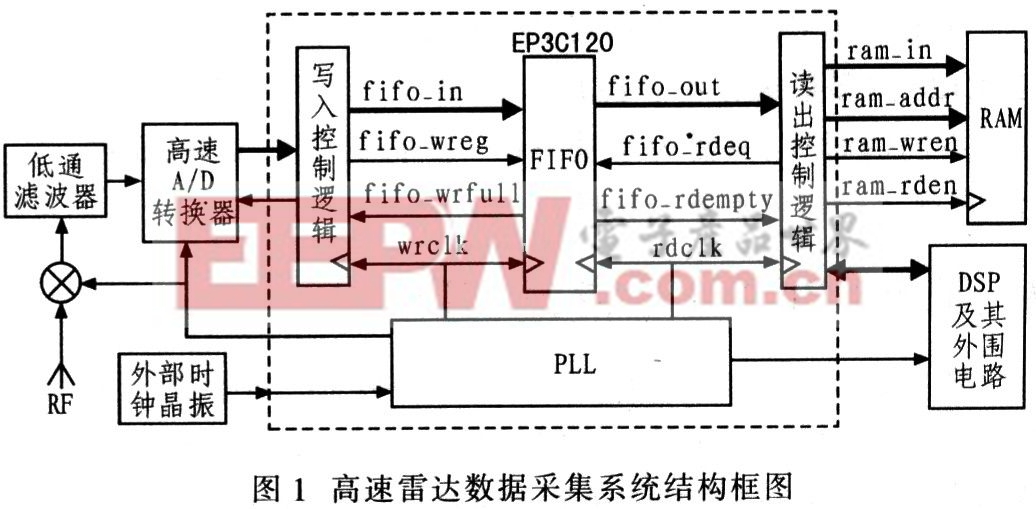

FPGA設計的高速FIFO電路技術,本文主要介紹高速FIFO電路在數據采集系統中的應用,相關電路主要有高速A/D轉換器、FPGA、SDRAM存儲器等。圖1為本方案的結構框圖。在大容量高速采集系統項目的開發過程中,FPGA作為可編程邏輯器件,設計靈活、可操作性

關鍵字:

電路 技術 FIFO 高速 設計 FPGA

在基于ARM的超聲波測厚系統中,ARM處理器的數據接收能力往往與A/D芯片的工作速率不匹配,為避免有效數據丟失,提高系統工作效率,用FIFO作為高速A/D與ARM處理器之間的中轉接口會得到很好的效果。這里以FIFO存儲器CY7C4261作為中轉器件實現了A/D芯片AD9283與ARM處理器S3C2410的接口設計,并敘述了數據從A/D芯片到ARM的整個數據采集過程。該接口電路用FIFO實現了超聲測厚系統中A/D與ARM之間的無縫連接,提高了系統測厚精度。它的電路簡單,調試方便,具有較高的應用價值。 關鍵字:

FIFO ARM 系統 接口設計

給出異步FIFO電路在高速數據采集系統中的應用,由FPGA生成獨立時鐘域的FIFO緩存器,采用FIFO的可編程設置參數啟動數據傳輸,根據讀寫時鐘頻率異同的傳輸要求和FIFO的特性,采用一套控制電路,解決了可變速率數據緩存和固定時鐘傳輸的問題。

關鍵字:

FIFO FPGA 時鐘 201004

高速異步FIFO的設計與實現,引言 現代集成電路芯片中,隨著設計規模的不斷擴大.一個系統中往往含有數個時鐘。多時鐘帶來的一個問題就是,如何設計異步時鐘之間的接口電路。異步FIFO(First In First Out)是解決這個問題的一種簡便、快捷的解

關鍵字:

實現 設計 FIFO 異步 高速

異步FIFO和PLL在高速雷達數據采集系統中的應用,將異步FIFO和鎖相環應用到高速雷達數據采集系統中用來緩存A/D轉換的高速采樣數據,解決嵌入式實時數據采集系統中,高速采集數據量大,而處理器處理速度有限的矛盾,提高系統的可靠性。根據FPGA內部資源的特點,將FIFO和鎖相環設計在一塊芯片上。因為未使用外掛FIFO和PLL器件,使得板卡設計結構簡單,并減少硬件板卡的干擾。由于鎖相環的使用,使得整個采集系統時鐘管理方便。異步FIFO構成的高速緩存具有一定通用性,方便系統進行升級維護。

關鍵字:

數據采集 系統 應用 雷達 高速 FIFO PLL 異步

fifo介紹

采用FIFO方式時,信息被以所收到的次序進行傳輸。

表示信息存儲的一種數據結構,含義是先進入的對象先取出。隊列(Queue )就是基于這種性質實現的。

FIFO( First In First Out)簡單說就是指先進先出。由于微電子技術的飛速發展,新一代FIFO芯片容量越來越大,體積越來越小,價格越來越便宜。作為一種新型大規模集成電路,FIFO芯片以其靈活、方便、高效的特性,逐漸在高速數據采 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473