- 同步時鐘信號是分布式錄波器系統任務順利完成的關鍵。介紹一種利用可編程CPLD器件實現性能優良的分布式同步信號源。通過高度集成,將IRIG-B(DC)解碼器以及系統的各種同步邏輯電路集成在一個MAXII570芯片中,構成一個高精度同步系統,從而達到最佳同步效果。

- 關鍵字:

分布式同步邏輯 IRIG-B CPLD

- 時間的精確和統一是變電站自動化系統的最基本要求。只有電力系統中的各種自動化設備(如故障錄波器、繼電保護裝置、RTU微機監控系統等)采用統一的時間基準,在發生事故時,才能根據故障錄波數據,以及各開關、斷路器動

- 關鍵字:

通信報文對時 GPS IRIG-B碼對時 繼電保護

- 引言隨著電子技術的發展,對遙測信號的幀結構的可編程度、集成度的要求越來越高,用于時間統一系統的B碼源的設計也趨于高度集成化。為了適應現代靶場試驗任務的要求,我們采用Altera的CPLD器件,將用于產生B碼的各種

- 關鍵字:

CPLD 時間統一系統 IRIG-B碼

- 摘要:基于ATmega8單片機設計出一種簡單、可靠、低成本的H碼(DC)解碼器。通過標準RS485接口接收差分H碼信號,信號經隔離后通過單片機解碼程序處理,轉換成標準時間碼(時分形式)通過無線方式發送給其他設備。此設計增

- 關鍵字:

IRIG-H ATmega8 nRF905 無線 解碼

- 摘要 針對基于單片機的IRIG—B碼解碼器解碼精度低、工作穩定性差等問題,提出了一種基于FPGA的IRIG—B碼解碼器設計。在實現過程中著重分析了輸

- 關鍵字:

IRIG―B碼 解碼 毛刺

- 為了實現靶場時統終端輸出IRIG-B標準DC code信號,采用VHDL語言在FPGA邏輯電路中設計了DC code編碼器硬件電路,通過QuartusⅡ軟件建立工程文件對VHDL語言DC code編碼器電路進行編譯和仿真,獲得了符合IRIG-B標準的DC code信號。經過實踐驗證,該電路具有實現方法簡單、電路穩定性好、精度高的特點,實測同步精度小于1μs。

- 關鍵字:

IRIG-B FPGA code VHDL

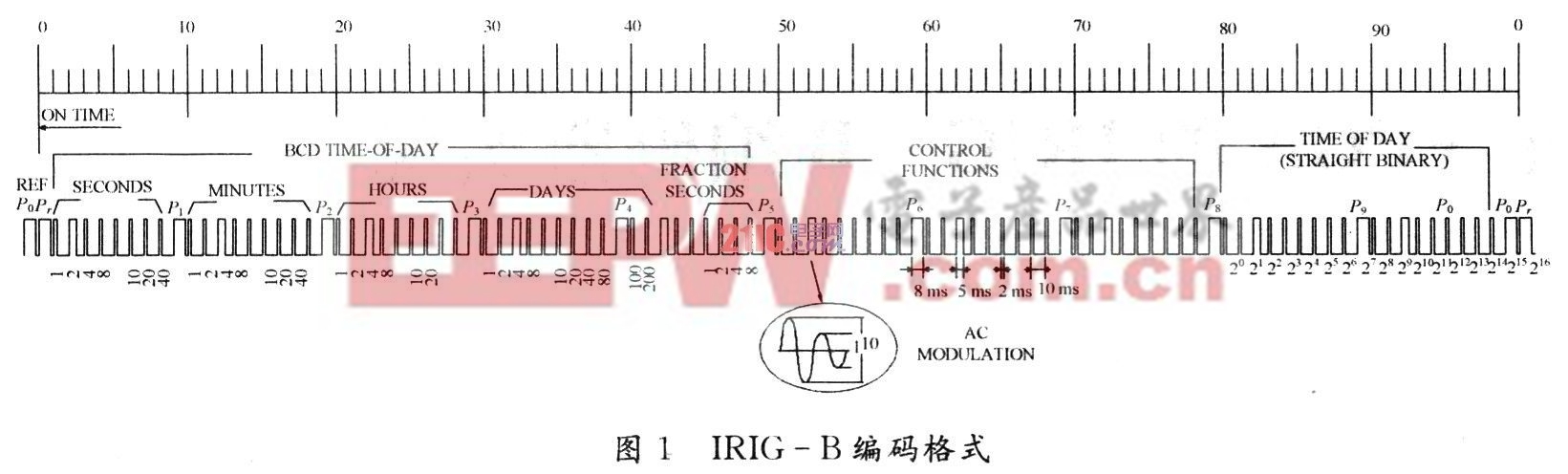

- 我國靶場測量、工業控制、電力系統測量與保護、計算、通信、氣象等測試設備均采用國際標準IRIG-B格式的時間碼(簡稱B碼)作為時間同步標準。B碼是一種串行的時間格式,分為直流碼(DC碼)和交流碼(AC碼)兩種,其格式和碼

- 關鍵字:

IRIG-B FPGA 編碼器

- 摘要:在分析武器裝備靶場試驗測控設備同步技術現狀基礎上,提出了一種多功能內置式IRIG-B碼終端設計;給出了終端的組成、功能與工作過程,詳細介紹了IRIG-B碼采集模塊、IRIG-B碼產生模塊和軟件模塊的設計;終端具有

- 關鍵字:

設計 終端 IRIG-B 內置 多功能

- 摘要:在分析了IRIG-B(DC)碼碼型特點的基礎上,提出了一種IRIG-B(DC)時間碼解碼的設計方法。該方法由少量外圍電路與一片現場可編程門陣列(FPGA)芯片組成,來實現對IRG-B(DC)碼的解碼、1 PPS信號輸出、實時時間顯示以

- 關鍵字:

IRIG-B FPGA DC 解碼

- 摘要:隨著變電站自動化技術的發展,對變電站內時間的精確和統一提出了更高的要求。本文提出了一種采用IRIG-B時間碼來時時的方案。在這種對時方案中,每個變電站只安裝一個GPS接收裝置,利用RS422/485總線傳輸IRIG-

- 關鍵字:

IRIG-B 對時方式 繼電保護裝置 中的應用

- 為達到IRIG-B碼與時間信號輸入、輸出的精確同步,采用現代化靶場的IRIG-B碼編碼和解碼的原理,從工程的角度出發,提出了使用現場可編程門陣列(FPGA)來實現IRIG-B碼編碼和解碼的設計方案和體系結構,設計中會涉及到幾個不同的時鐘頻率,FPGA對時鐘的同步性具有靈活性、效率高、且功耗低。抗干擾性好的特點。結果表明,FPGA能夠確保為從設備提供同源的時鐘基準,使時鐘與信號的延遲控制在200 ns以內,從而得到了IRIG-B碼與時間精確同步的效果。

- 關鍵字:

IRIG-B FPGA DC 編碼

- 摘要:提出了一種IRIG-B(DC)碼產生電路的設計方法。采用Altera公司低功耗Cyclone FPGA系列中的EPlC6T144、8段數碼管、晶體振蕩器和MAX3232E等器件構成硬件電路、使用VHDL語言設計IRIG-B直流時間碼的軟件。為了設置和

- 關鍵字:

IRIG-B FPGA DC 產生電路

- 摘要:旨在設計一款基于FPGA的IRIG-B時間系統。該系統采用FPGA作為控制器,GPS引擎M12T作為標準時鐘源,利用M12T輸出的100 pps信號觸發IRIG-B編碼模塊,完成DC碼編碼。在DC碼的基礎上,通過正弦查找表實現了IRIG-B交

- 關鍵字:

實現 編碼器 IRIG-B FPGA 基于 FPGA

irig-b碼對時介紹

您好,目前還沒有人創建詞條irig-b碼對時!

歡迎您創建該詞條,闡述對irig-b碼對時的理解,并與今后在此搜索irig-b碼對時的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473