???? 近兩年,國際上大的半導體公司都推出了65納米產品,并開始了45納米/40納米產品的研發,而國內也已經有五六家企業開始了65納米的設計。但總體來說,65納米/40納米設計目前仍然還是一個新生事物,企業要解決一系列的技術難題。為此,我們邀請FPGA企業、EDA企業、IP企業、芯片制造企業共同探討新工藝技術的研發關鍵點。

?

????主持人?趙艷秋

?

??&nbs

關鍵字:

半導體 FPGA 功耗 功率管理 Altera 65納米

由Altera公司主辦的SOPC WORLD大會在深圳舉行,Altera亞太區副總裁兼董事總經理Erhaan Shaikh在大會上作了“多處理技術提高性能,降低功耗”的主題演講。

Shaikh說:“功耗管理對未來應用非常關鍵,功耗挑戰的一個例子就是每個移動基站每年耗電大約20,000公斤柴油。”為此,必須從提高性能、降低功耗并降低成本這三個方面來滿足未來應用的需要。他強調說,“Altera的構建未來的解決方案就是Stratix IV E

關鍵字:

Altera 功耗 FPGA 中興通信 IBM

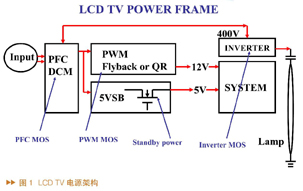

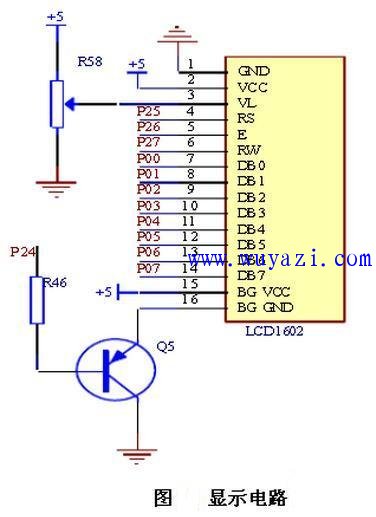

LCD TV電源架構的介紹

圖1所示為LCD TV的電源架構,圖中架構的輸入電壓為90-265V,輸入頻率從47Hz到63Hz,經過調試整流后會經過PFC架構,由于本文主要針對MOS,因此圖中沒有表示出調試整流部分。PFC根據所使用的IC選擇采用DCM或者CCM。從PFC出來后有一個PWM,如果輸出功率小于65W,則PWM端采用Flyback或QR模式。現在LCD TV常用的是半橋共振和LLC架構。5V一側有備用電源,目前LCD TV的備用電源通常采用的是IC綁定MOS。所不同的是逆變器部分,傳

關鍵字:

LCD TV 電源 功耗

內存是PC機重要的部件之一,一般而言,每代內存規格的生命周期為3-5年,如今DDR2規格在經歷了4年左右的發展后,已經進入了其生命的最后歷程。

隨著電腦技術以及應用軟件的不斷進步,在各種應用當中, DDR2內存無論在性能還是功耗上對現今以及未來的需求都顯的有些捉襟見肘。作為IT行業的領跑者,在Intel現階段以及今后的發展藍圖中,我們可以看見DDR3內存正逐漸取代DDR2。

作為即將取代DDR2規格內存的DDR3,相比DDR2頻率上限更高且電壓更低,這些改進能為我們帶來什么好處呢?

關鍵字:

DDR3 Windows Vista 功耗 內存 DDR2

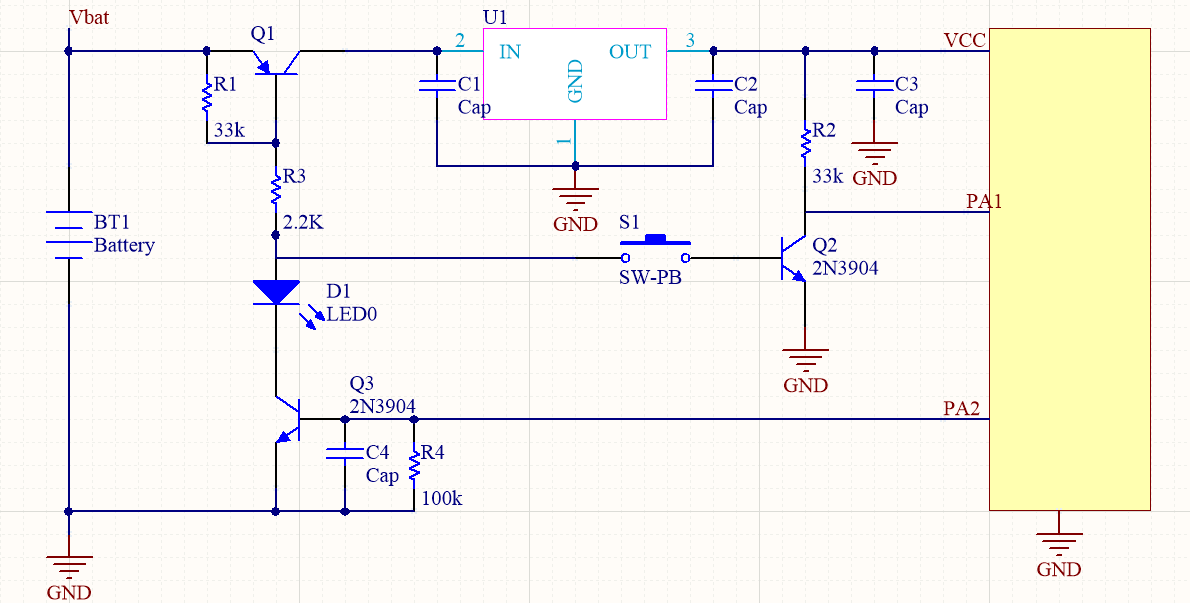

介紹了由低功耗大容量Flash閃速存儲器K9K2G08及低功耗單片機MSP430F149等組成的微型低功耗大容量心電記錄儀的設計,有效地解決了Holter需要大存儲容量與低功耗的問題。該記錄儀可完整地記錄超過200小時的心電信息,具有體積小、功耗低的特點,可在需要的時候將數據傳送到PC機中查看和分析心電圖,特別適合于家庭監護和心電短暫異常病人的疾病診斷。

關鍵字:

記錄儀 研制 心電 大容量 功耗 微型

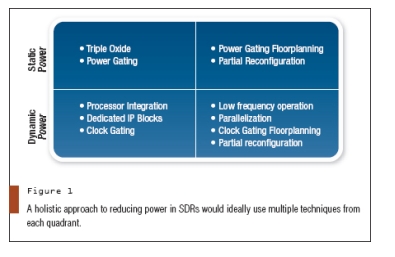

由于像美國聯合戰術無線電系統(JTRS)這樣的計劃,軟件定義的無線電(SDR)早已被證實。然而,有許多問題嚴重地制約著SDR的廣泛部署,其中相當重要的問題就是功率。

功率是在設計每一個SDR子系統時的主要考慮因素,特別是因為它們要消耗比硬件無線電更多的功率。例如,為了獲得預期的無線電通信距離(依賴于鏈路的狀況,典型值為5-10千米數量級),射頻(RF)前端必須具備足夠的發射功率。同樣,對于靠電池工作的無線電設備,RF前端、調制解調器和加密處理子系統的功耗都直接影響無線電設備的壽命。此外,對由調制

關鍵字:

FPGA 無線電 SDR 功耗

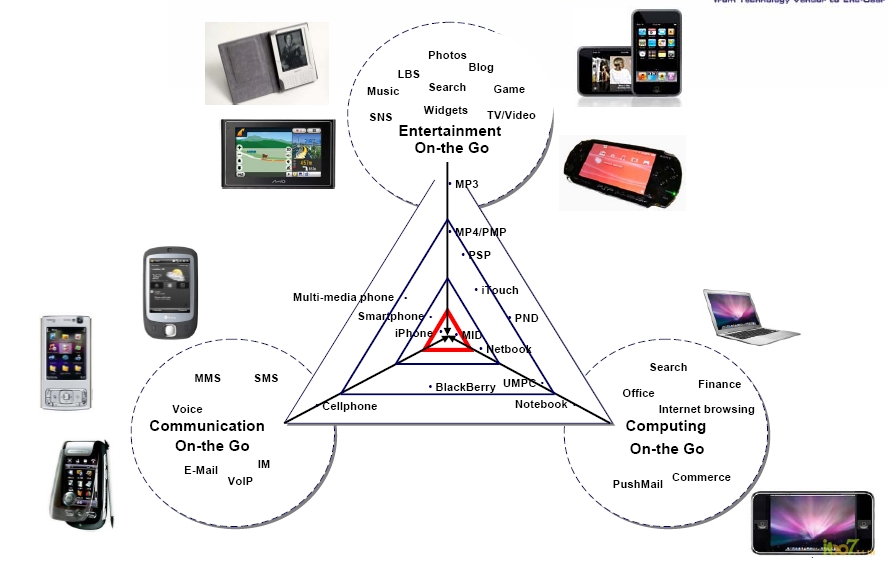

目前,便攜式產品已經深入到我們生活的方方面面,成為引領半導體產業前進的主導力量,另一方面,便攜式產品種類也日益繁多,MP3、MP4、PMP、UMPC、PND、MID、移動電視終端等便攜式新品不斷涌現,同時便攜式功能日益強大,不但能提供音頻、視頻播放等娛樂功能,還能提供導航、上網、商務等功能,在便攜式產品日新月異的同時,一個個疑問也開始困擾便攜式設計工程師:未來便攜式產品會融合嗎?如何融合?融合哪些功能?如何應對便攜式產品的電源管理挑戰?2008年7月17~18日,在深圳創意時代主辦的“PD

關鍵字:

便攜式產品 Linux 3M投影 飛兆半導體 功耗 意法半導體 電源 CMMB

功耗關

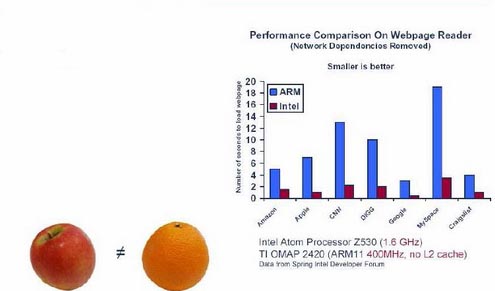

其次,功耗更低。ARM是以低功耗和近乎福利價的IP(知識產權)授權走遍天下的。Intel的功耗不低,為此推出了多核戰略。不僅如此,今年三季度(9月10日左右),Intel將推出第一個針對嵌入式市場的芯片:SoC(系統芯片)處理器“Tolapai”。實現了兩年前的承諾:集成了北橋和南橋。Tolapai處理器基于改良版的Pentium M核心,32-bit設計,頻率600MHz、1GHz、1.2GHz,采用65nm工藝制造,集成1.48億個晶體管,封裝面積37.5×37.5mm,熱設計功耗1

關鍵字:

Intel 嵌入式 功耗 SoC ARM

直到最近,異步電路僅僅在非常必要時才使用。由于學術界的偏見,它們通常被視為邊緣產品。現在,許多商用設備已經開發了上述針對各類小眾市場的功能。

關鍵字:

功耗 高性能 設計 核心 DSP 異步

降低便攜式應用的功耗,無線手持終端設備、智能電話、PDA 以及媒體播放器等新一代便攜式消費類電子產品均具有更多的特性和更高的性能,通常其尺寸也變得更小巧。由于這些最新的特性,這些設備均要求極高的功耗。

關鍵字:

功耗 應用 便攜式 降低 德州儀器

基于ARM CPU并集成了外圍功能(如實時操作系統定時器等)的μPLAT系列是一種基本系統級LSI開發平臺。高速及低功耗的μPLAT-92平臺專為W-CDMA、PDA及其它便攜式終端(如互聯網設備)應用而開發。μPLAT-92是以硬IP為特征的硬件開發與集成環境的平臺總稱:μPLAT-92內核包括一顆ARM920T CPU及運行操作系統所需的最少外圍I/O器件;電源管理IP及原型板也包括在內。這不僅能提高系統級LSI的運行速度及降低其功耗,而且還能縮短規模不斷提高的大型系統級LSI的開發時間,并使用戶能專

關鍵字:

功耗 微型 平臺 高速 開發 系統 LSI 面向

由于目前大部分能源是從化石燃料取得,過度地消耗石油等能源,引發了環境問題、經濟問題和政治問題等,使我們的世界不那么美好了。

半導體如何幫助解決能耗?

過去20年,功耗一直在上升,而不是下降。摩爾定律出什么錯了?因為功耗!每個晶體管的單位功耗下降了,這毫無疑問。但是每個芯片的晶體管數量增長更快,因此導致芯片的總功耗增加。一年前,Intel發明了45nm的工藝-以Hf(鉿)為基礎的High-k(高k)材料作為絕緣層材料,代替了傳統的二氧化硅,大幅減少漏電量。但是沒有完全解決問題,因為在電路中功

關鍵字:

功耗 半導體 能耗 新能源 200806

目前,處理器性能的主要衡量指標是時鐘頻率。絕大多數的集成電路 (IC) 設計都基于同步架構,而同步架構都采用全球一致的時鐘。這種架構非常普及,許多人認為它也是數字電路設計的唯一途徑。然而,有一種截然不同的設計技術即將走上前臺:異步設計。

關鍵字:

功耗 高性能 設計 核心 DSP 異步

這一新技術的主要推動力來自硅技術的發展狀況。隨著硅產品的結構縮小到 90 納米以內,降低功耗就已成為首要事務。異步設計具有功耗低、電路更可靠等優點,被看作是滿足這一需要的途徑。

關鍵字:

功耗 高性能 設計 核心 DSP 異步

ABI Research的最新研究報告指出,RFID讀取器正在向高度集成化和創新性發展。

讀取器電路中的低頻 (LF) 和高頻 (HF) RFID電路由于能夠與體積更小功耗更低的器件集成,正在成為市場的領先器件。類似的集成化趨向在超高頻 (UHF) RFID 讀取器電路也在進展中,集成有第一代UHF讀取器電路的產品正在走向市場。

ABI Research的主任分析師Pete Poorman說:“EPCglobal Gen 2 無源UHF RFID 標準實踐證明性能可靠,

關鍵字:

RFID ABI 功耗 集成化

90w 功耗介紹

您好,目前還沒有人創建詞條90w 功耗!

歡迎您創建該詞條,闡述對90w 功耗的理解,并與今后在此搜索90w 功耗的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473