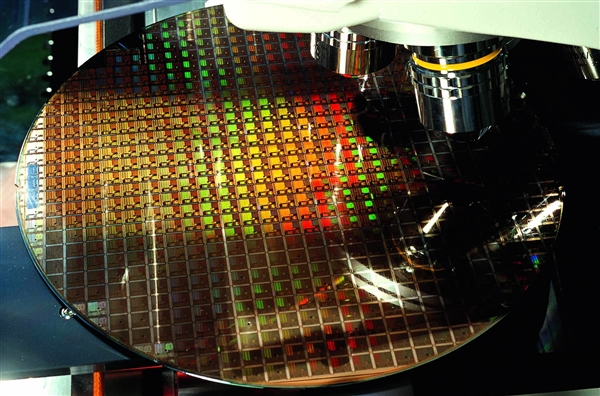

- 盡管2020年全球半導體行業會因為疫情導致下滑,但臺積電的業績不降反升,掌握著7nm、5nm先進工藝的他們更受客戶青睞。今天的財報會上,臺積電也首次正式宣布3nm工藝詳情,預定在2022年下半年量產。臺積電原本計劃4月29日在美國舉行技術論壇,正式公布3nm工藝詳情,不過這個技術會議已經延期到8月份,今天的Q1財報會議上才首次對外公布3nm工藝的技術信息及進度。臺積電表示,3nm工藝研發符合預期,并沒有受到疫情影響,預計在2021年進入風險試產階段,2022年下半年量產。在技術路線上,臺積電評估多種選擇后

- 關鍵字:

三星 CPU處理器 臺積電 3nm

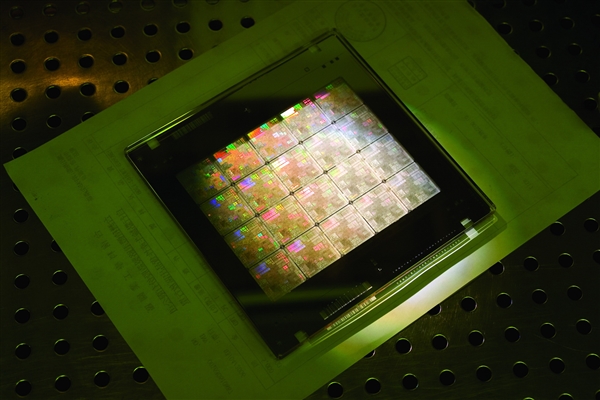

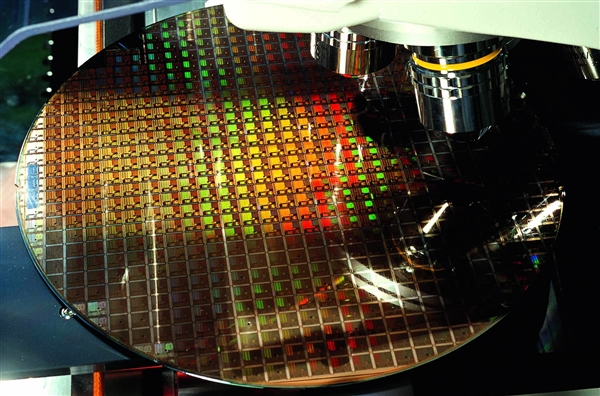

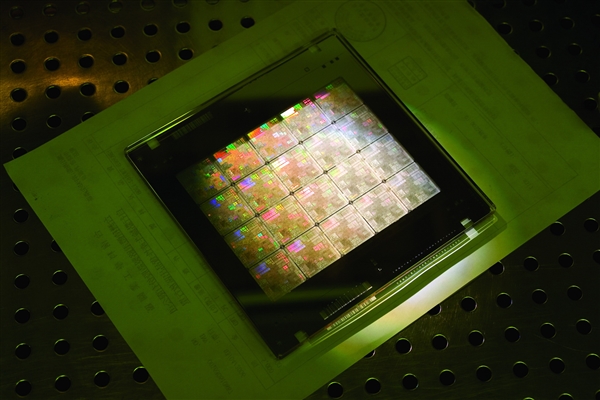

- 據國外媒體報道,在芯片制造工藝方面走在行業前列的芯片代工商臺積電,在2018年率先量產7nm芯片之后,今年將大規模量產5nm芯片,外媒此前的報道顯示,臺積電今年4月份就將開始為相關客戶大規模生產5nm芯片。在7nm投產已兩年、5nm工藝即將大規模量產的情況下,臺積電也將注意力放在了更先進的3nm工藝上。在最新的報道中,外媒就提到了臺積電3nm工藝方面的消息,其表示今年10月份,臺積電就將開始安裝生產3nm芯片的設備。3nm工藝是5nm之后,芯片制造工藝的一個重要節點。在2019年第四季度的財報分析師電話會

- 關鍵字:

臺積電 3nm

- 很快,臺積電和三星的5nm工藝即將量產,與此同時,臺積電和三星的3nm工藝也在持續的研發當中。而對于5nm及以下工藝來說,都必須依靠EUV(極紫外)光刻機才能實現。而目前全球只有一家廠商能夠供應EUV光刻機,那就是荷蘭的ASML。很快,臺積電和三星的5nm工藝即將量產,與此同時,臺積電和三星的3nm工藝也在持續的研發當中。而對于5nm及以下工藝來說,都必須依靠EUV(極紫外)光刻機才能實現。而目前全球只有一家廠商能夠供應EUV光刻機,那就是荷蘭的ASML。目前ASML出貨的EUV光刻機主要是NXE:340

- 關鍵字:

3nm EUV

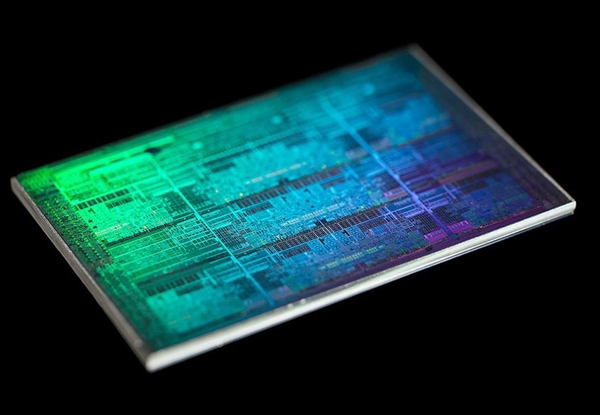

- 在燧原科技(燧原)發布云燧T10之際,燧原與格芯(GLOBALFOUNDRIES)近日共同宣布推出針對數據中心培訓的高性能深度學習加速卡解決方案,其核心“邃思”(DTU)基于格芯12LP?FinFET平臺及2.5D 封裝技術,為云端人工智能訓練平臺提供高算力、高能效比的數據處理。燧原的“邃思”(DTU)利用格芯12LP ?FinFET平臺擁有141億個晶體管,采用先進的2.5D封裝技術,支持PCIe 4.0接口和燧原 Smart Link高速互聯。支持CNN/RNN等各種網絡模型和豐富的數據類型

- 關鍵字:

FinFET 2.5D

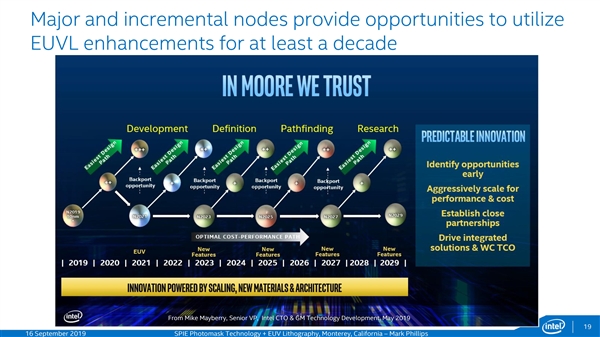

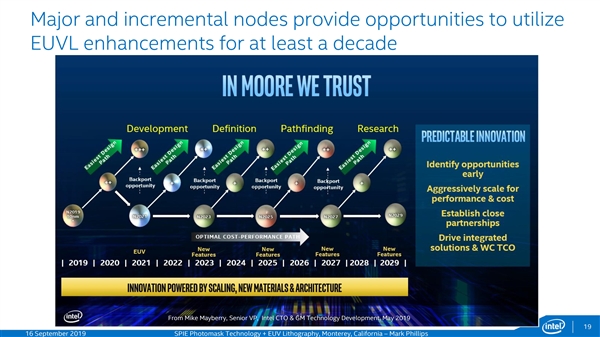

- 原文流傳年的幻燈片并非出自Intel官方,而是荷蘭光刻機巨頭ASML在Intel原有幻燈片基礎上自行修改的,5nm、3nm、2nm、1.4nm規劃均不是出自Intel官方,不代表Intel官方路線圖。Intel官方原始幻燈片如下:在IEDM(IEEE國際電子設備會議上),有合作伙伴披露了一張號稱是Intel 9月份展示的制造工藝路線圖,14nm之后的節點一覽無余,甚至推進到了1.4nm。讓我們依照時間順序來看——目前,10nm已經投產,7nm處于開發階段,5nm處于技術指標定義階段,3nm處于探索、先導階

- 關鍵字:

英特爾 10nm 7nm 5nm 3nm

- 臺積公司5奈米 FinFET 強化版(N5P)制程技術上開發的DesignWare PHY IP核包括USB、DisplayPort、DDR、LPDDR、HBM、PCI Express、Ethernet、MIPI和HDMI臺積公司N5P工藝上開發的DesignWare基礎IP核包括高速、面積優化和低功耗的嵌入式存儲器、邏輯庫和一次性可編程非易失性存儲器。STAR Memory System?采用針對5nm FinFET晶體管缺陷的新算法,可有效測試、修復和診斷嵌入式存儲器新思科技(Synopsys, In

- 關鍵字:

新思 臺積合 FinFET 強化版N5P

- 晶圓代工大廠格芯(GLOBALFOUNDRIES)宣布,與IC設計廠SiFive正在合作研發將高頻寬存儲器(HBM2E)運用于格芯最近宣布的12LP+FinFET解決方案,以擴展高性能DRAM。12LP+FinFET解決方案將提供2.5D封裝設計服務,可加速人工智能(AI)應用上市時間。

- 關鍵字:

格芯 人工智慧應用 12LP+ FinFET

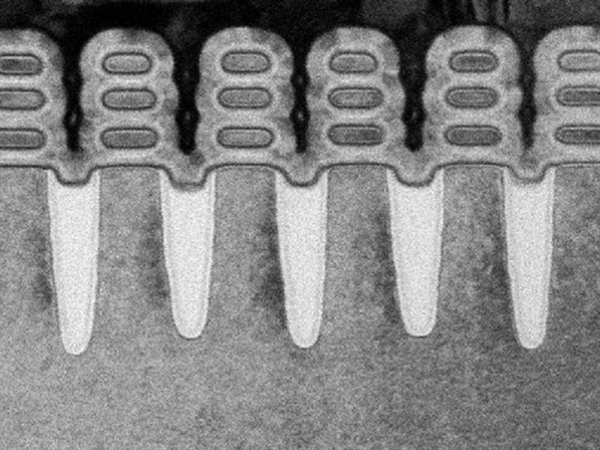

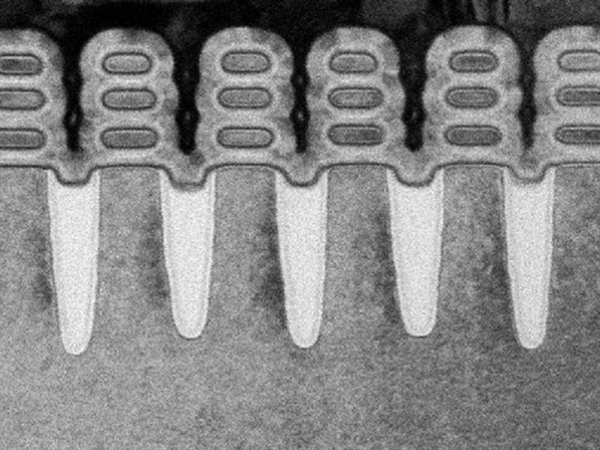

- 盡管日本嚴格管制半導體材料多少都會影響三星的芯片、面板研發、生產,但是上周三星依然在日本舉行了“三星晶圓代工論壇”SFF會議,公布了旗下新一代工藝的進展,其中3nm工藝明年就完成開發了。三星在10nm、7nm及5nm節點的進度都會比臺積電要晚一些,導致臺積電幾乎包攬了目前的7nm芯片訂單,三星只搶到IBM、NVIDIA及高通部分訂單。不過三星已經把目標放在了未來的3nm工藝上,預計2021年量產。在3nm節點,三星將從FinFET晶體管轉向GAA環繞柵極晶體管工藝,其中3nm工藝使用的是第一代GAA晶體管

- 關鍵字:

CPU處理器,3nm

- 如今在半導體工藝上,臺積電一直十分激進,7nm EUV工藝已經量產,5nm馬上就來,3nm也不遠了。臺積電CEO兼聯席主席蔡力行(C.C. Wei)在投資者與分析師會議上透露,臺積電的N3 3nm工藝技術研發非常順利,已經有早期客戶參與進來,與臺積電一起進行技術定義,3nm將在未來進一步深化臺積電的領導地位。目前,3nm工藝仍在早期研發階段,臺積電也沒有給出任何技術細節,以及性能、功耗指標,比如相比5nm工藝能提升多少,只是說3nm將是一個全新的工藝節點,而不是5nm的改進版。臺積電只是說,已經評估了3n

- 關鍵字:

臺積電 3nm

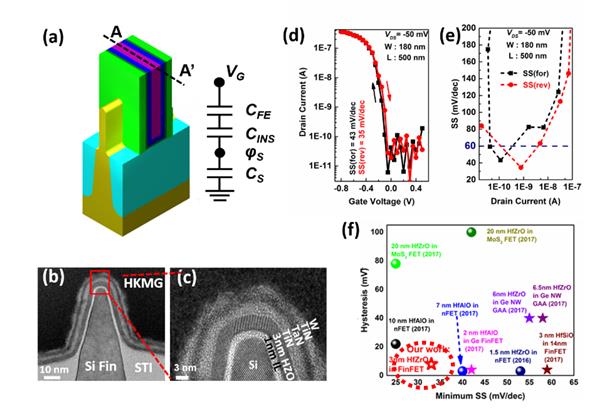

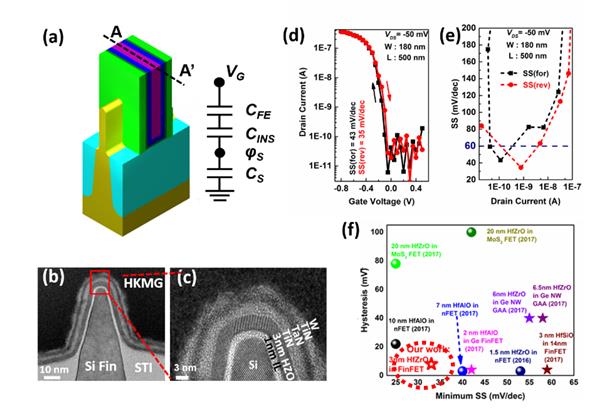

- 今天有多家媒體報道了中國科研人員實現了3nm半導體工藝的突破性進展,香港《南華早報》稱中科院微電子所團隊的殷華湘等人研究出了3nm晶體管,相當于人類DNA鏈條寬度,這種晶體管解決了玻爾茲曼熱力學的限制。

- 關鍵字:

3nm 半導體

- 作為全球晶圓代工市場的一哥,臺積電一家就占了全球50-60%的份額,幾乎吃下所有7nm先進訂單。不過今年遇到了半導體市場熊市,臺積電Q1季度營收、盈利也不免受影響下滑,凈利潤暴跌了32%。不過臺積電今年依然要砸錢研發新工藝,預計會在7nm、5nm及3nm工藝研發上投資80億美元之多。

- 關鍵字:

臺積電 Q1 7/5/3nm

- 在智能手機、存儲芯片業務陷入競爭不利或者跌價的困境之時,三星也將業務重點轉向邏輯工藝代工。在今天的三星晶圓代工SFF美國分會上,三星宣布四種FinFET工藝,涵蓋了7nm到4nm,再往后則是3nm GAA工藝了,通過使用全新的晶體管結構可使性能提升35%、功耗降低50%,芯片面積縮小45%。

- 關鍵字:

三星 3nm

- 在半導體晶圓代工市場上,臺積電TSMC是全球一哥,一家就占據了全球50%以上的份額,而且率先量產7nm等先進工藝,官方表示該工藝領先友商一年時間,明年就會量產5nm工藝。在臺積電之外,三星也在加大先進工藝的追趕,目前的路線圖已經到了3nm工藝節點,下周三星就會宣布3nm以下的工藝路線圖,緊逼臺積電,而且會一步步挑戰摩爾定律極限。

- 關鍵字:

三星 臺積電 3nm

- 科技的發展有時超出了我等普通人的想象,今年臺積電才開始量產7nm,計劃明年量產5nm,這不3nm又計劃在2022年實現量產,這樣的大踏步前進可以說是競爭爭奪激烈的結果、也是科技快速發展的結果。

- 關鍵字:

3nm 臺積電

- Mentor, a Siemens business 今日宣布 Mentor Calibre? nmPlatform 和 Analog FastSPICE? (AFS?) Platform 獲得 TSMC 的 7nm FinFET Plus 和最新版本的 5nm FinFET 工藝的認證。此外,Mentor 還繼續擴展 Xpedition? Package Designer 和 Xpedition Substrate Integrator 產品的功能,以支持 TSMC 的高級封裝產品。 TSMC 設

- 關鍵字:

Mentor FinFET

3nm finfet介紹

您好,目前還沒有人創建詞條3nm finfet!

歡迎您創建該詞條,闡述對3nm finfet的理解,并與今后在此搜索3nm finfet的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473