2.4GHz頻段的射頻信號發生器設計(07-100)

前言

本文引用地址:http://www.czjhyjcfj.com/article/92063.htm在現代無線通信系統中,對大容量、高速數據的無線傳輸提出越來越高的要求,許多廠商也推出基于802.11系列協議的射頻IC,并且無線路由器、藍牙等技術的廣泛應用,對2.4GHz頻段的使用需求日益增多,但是除部分高端信號發生器具有2.4GHz頻段的信號產生,大多數普通信號發生器均未涉及2.4GHz頻段,開發涉及一種基于2.4GHz頻段的射頻信號發生器以滿足科研及教學儀器使用的需要。本文正是基于這一點,設計成本低、性能可靠的2.4GHz頻段的射頻信號發生器。

系統方案

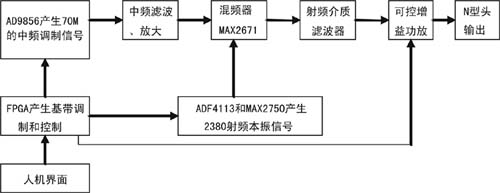

系統方案以儀器面板上的人機控制設定所要操作的工作頻率和基帶調制方式,經由FPGA進行直接控制生成4種基本調制模式,即QPSK、16/64-QAM、GMSK、FSK,并將基帶I/Q兩路信號經由串并轉換后送入AD9856將信號調制至70MHz的中頻信號,然后通過上混頻器MAX2671混頻至2450MHz的射頻信號,然后將混頻后的信號送入射頻濾波器,再由可控增益放大器將信號輸出。

2.4GHz頻段的射頻信號發生器框圖如圖1所示。

電路設計

信號調制電路

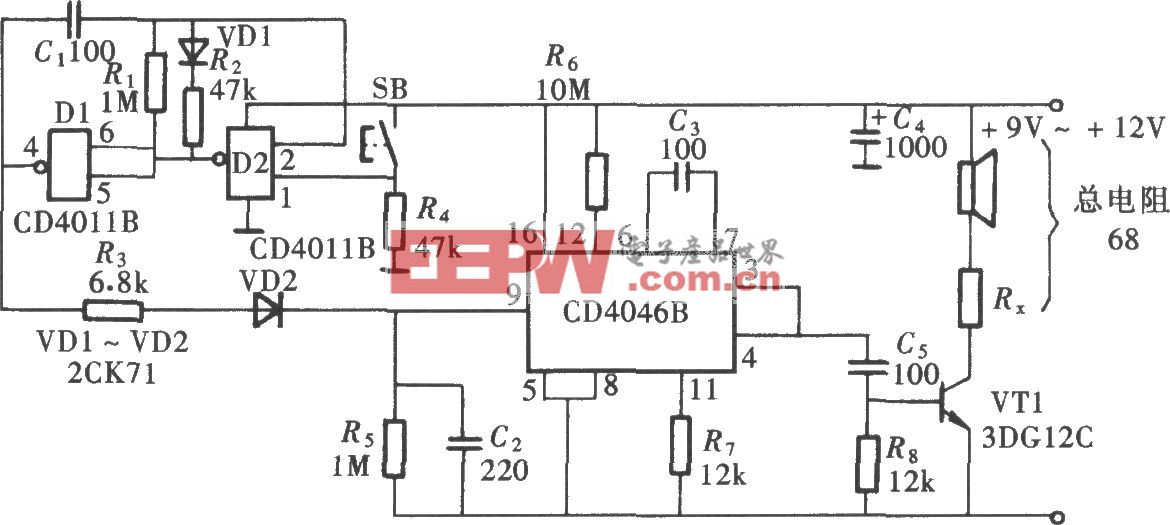

信號調制電路首先是FPGA電路設計采用ALTERA公司的EP1C20芯片,用VHDL編程實現由人機界面輸出控制信息,然后將控制信息對應所要產生的信號,將信號輸出到AD9856。AD9856是ADI公司的一款單片混合信號的12位積分數字上行轉換器,采樣速率為200MSPS,產生80MHz的數字輸出和80dB窄帶的無雜散信號動態范圍。AD9856具有200MHz的內部時鐘,集成帶鎖定指示器的4~20倍可編程時鐘倍頻器,提供高精度的系統時鐘,單端或者差分輸入參考時鐘,而且可以輸出數據時鐘;內部32位正交DDS,可實現FSK調制功能;12位DDS和DAC和數據路徑結構,可接受復合I/Q輸入數據;32位頻率控制字,采用與SPI兼容的接口,用FPGA控制可靠方便,串行時鐘為10MHz;具有反轉SINC功能,在DAC變換之前恢復出想得到的信號包絡。利用AD9856產生調制信號的電路框圖見圖2所示。

圖1系統框圖

評論