一種結構簡單的低壓低功耗ALU單元設計

1.引言

本文引用地址:http://www.czjhyjcfj.com/article/84709.htm隨著手持式個人通訊系統等的發展,低壓低功耗高吞吐量電路的需求越來越多,因此低功耗微處理器和元件的設計已經變成了主流。ALU是微處理器最重要的組成部分,其中全加器電路是所有運算電路的基本單元,設計低功耗快速加法器單元是獲得低功耗高速運算電路的關鍵。ALU單元的設計標準是多種多樣的,晶體管數量顯然是一個主要的關注點,因為它極大的影響了功能單元ALU的設計復雜性。另外兩個重要的卻又相互矛盾的因素是功耗和速度。與功耗降低相關的一個因素是電路能工作的最低電壓, 還有一個是晶體管的數量,而全加器晶體管的數量又極大的影響了ALU單元的晶體管數量,因此全加器的設計也是ALU設計中必須重點考慮的一部分。對于已有的全加器的設計按照種類來分【1-8】有靜態CMOS電路,動態電路,傳送管和傳輸門邏輯。其中全靜態CMOS電路是最傳統的,但需要28個管子。動態電路能極大的減少晶體管的數量但是短路功耗卻很大;使用傳送門邏輯是一個可選的降低電路復雜性的方案。在【1】中基于傳送門和反向器的全加器設計中各使用了20和16個晶體管,為了得到更少管子的全加器,在【2】中基于XOR/XNOR的傳送門邏輯電路組成的全加器只用了14個管子,在【3】中,介紹了一個基于傳輸管的靜態能量恢復全加器(SERE),它只使用了10個管子,且不管它自稱的功耗小,這個設計相比同類的設計來講速度比較慢,同時這個設計不能用來級連,因為在低電壓下工作時有多閥值損失問題。在【4】中一種新的基于選擇電路的10管全加器設計被提出,然而這個設計也同樣有多閥值損失問題,以至于不能在低電壓級連模式下正確的工作,前面提到的10管全加器都是基于圖1的原理來的。文中的ALU單元將采用一種新的10管全加器,它可以減輕閥值損失問題,這個設計可以在使用少量管子的情況下組成快速的并行加法器(RCA)同時保持較低的能量損耗,另外,這個設計可以在較低的工作電壓下正確運行。

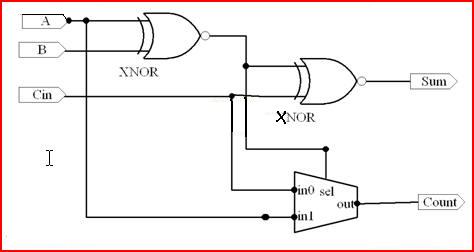

圖1 .現有的10管全加器結構

2.新的基于CLRCL全加器的ALU單元

首先考慮全加器的設計,全加器的邏輯表達式為:

Sum=(A⊙B)·Cin+(A⊕B) ·!Cin Count=(A⊕B) ·Cin+(A⊙B) ·A

可以看出有兩個基本的模型需要使用――XOR和2選1選擇器。一個XOR/XNOR功能用傳送門邏輯只用四個管子就可以達到【5】,一個2選1選擇器可以用兩個管子實現。但是這些電路都有不同程度的閥值電壓損失,所以在使用時必須小心,文中將采用一種新的全加電路,這個全加器的特點是進位邏輯電平恢復稱之為(Complementary and Level Restoring Carry Logic or CLRCL)。目的是為了減小電路的復雜性和達到快速的級連運作。為了避免進位鏈的多閥值電壓損失,為此重寫全加器的和以及進位邏輯公式:

Sum =(A⊕Cin) ·!Cout+(A⊙Cin) ·B Count =(A⊕Cin) ·B+(A⊙Cin) ·A

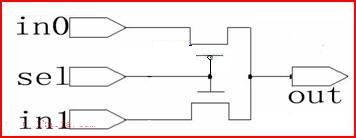

改進后的電路圖如圖2.其中MUX的電路如圖3所示。這樣設計的合理之處在于以下幾點:首先,避免了使用有閥值損失的信號作為下一個單元的控制信號,這是在現有的10管全加器中普遍存在的問題,這將導致在電路級連的時候有多閥值電壓損失從而使電路不能正確工作;第二,在傳送管鏈中去除了沒有緩沖的進位信號傳送。根據Elmore公式,傳送延遲時間跟級連的傳送門數目是二次方的關系【6】。即使是中等數目的級連長度,這樣的延遲也是不能忍受的。

圖2.新的1位ALU單元電路圖

圖3 .MUX 的MOS電路圖

正如圖2中全加器部分電路所示,XNOR電路采用了一個2選1選擇器加一個反向器來實現,這個反向器的功用有三個:第一,反向器INV1可以用來補償輸出傳送門輸出電壓的損失,這個輸出將用來與另外兩個2選1選擇器一起實現和以及進位功能,這樣和以及進位信號的閥值電壓損失可以控制在一個|V t|;第二,反向器INV2在進位鏈中充當了一個緩沖器的作用,從而加速了進位的傳送;第三,同時這個反向器提供了一個進位的互補信號(!Count)供下一級電路使用。這樣全部的全加器部分電路就只需要10個管子(5個PMOS和5個NMOS),這是目前我們所知的最少的實現全加器電路的晶體管數目。

評論