基于最佳接收的UART的設計與實現

在嵌入式系統設計中常使用通用異步接收和發送器UART(Universal Asynchronous Receiver/Transmitter)實現系統控制信息或低速數據信息的傳輸,而UART所采用的奇偶校驗方式不具備前向糾錯能力,檢錯能力也有限,所以在設計UART時要盡可能提高其抗干擾能力,以加強系統的可靠性。

本文引用地址:http://www.czjhyjcfj.com/article/83208.htm1 基于最佳接收的UART

目前UART中的接收器多采用如圖1所示的設計。

同步模塊的作用是檢測異步串口的同步位(Sync位)并提取抽樣判決需要的采樣信號,使抽樣判決模塊盡量在輸入信號RXD的碼元中部對信號采樣(如圖2)。因為信號在碼元邊沿跳變時會有振鈴或過沖等抖動,所以碼元的邊沿部分不適合采樣。要想獲得較佳的抽樣判決效果,最好在靠近碼元中部的位置對接收到的信號進行抽樣判決。

這種在碼元中部進行抽樣判決的接收方法可以有效去除振鈴、過沖等信號的邊沿抖動帶來的影響,但無法解決隨機脈沖干擾帶來的問題。如圖3所示,隨機脈沖干擾可能在任何時刻出現。即使同步模塊工作正常,使得抽樣判決總處在碼元中部的最佳采樣時刻,也有可能由于隨機脈沖干擾造成判決錯誤。

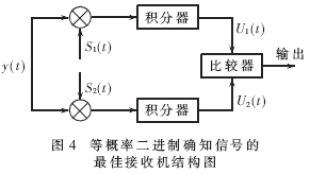

為了盡可能地減弱隨機干擾及其他干擾給信號接收帶來的影響,引入最佳接收機結構來設計UART的接收器,以實現信號的最佳接收。等概率二進制確知信號(異步串口通信的信號即屬于此情況)的最佳接收機結構如圖4所示。

圖4中的乘法器和積分器實質上構成了一個相關器,因此上述結構又稱為相關器形式的最佳接收機。其中相關器的輸出u(t)由下式定義:

其中:T為采樣周期,N表示一個碼元的時間包含N個采樣周期。

U1(kT)和U2(kT)由上式計算可得,然后送到比較器在最佳判決時刻(t=kNT)進行比較,若U1(kT)≥U2(kT),則判決為邏輯1,否則判決為邏輯0。

UART接收器接收的信號是未經調制的二進制基帶信號,碼元波形不是高電平就是低電平,兩種碼元的波形截然不同。因此,如果輸入信號Y(nT)與S1(kT)相關運算的結果較大,則Y(nT)與S2(kT)相關運算的結果就很小;反之亦然。所以可以將上述最佳接收機結構中S2(kT)這一路相關器省略,只保留一路相關器。最后的比較器改成判決器,判決準則是:如果相關器在最佳判決時刻(t=kNT)的輸出大于某個閾值,則判決為邏輯1;否則判決為邏輯0。經過簡化改進基于最佳接收機結構的UART接收器的框圖如圖5所示。

下面以一個簡單示例證明基于最佳接收的UART接收器可以有效地去除隨機干擾給信號接收帶來的影響。如圖6所示,在這個碼元周期內,如果采用一次抽樣判決,則即使處于一次抽樣判決的最佳采樣時刻,也會由于隨機脈沖干擾而產生誤判;如果引入數字相關器在最佳判決時刻進行判決,則盡管由于信號邊沿的抖動和隨機脈沖的干擾,信號的波形遭到了破壞,但信號在碼元周期內相關運算的結果為7,大于閾值5,接收器依然能正確地判定接收到的信號為邏輯1。這將有效抑制隨機干擾給信號接收帶來的影響。

2 基于FPGA的UART設計優化

數字相關器的引入,極大地提高了UART接收器的抗干擾性能,但也帶來了兩個問題:

(1)在數字相關器輸出相關運算的結果后,判決器需要在最佳判決時刻進行判決,因為此時與信號的相關輸出最大。同步模塊得到的判決信號與這個最佳判決時刻的偏移越大,UART接收器的性能就越差。也就是說,數字相關器對同步模塊的判決信號有很高的精確度要求。

(2)數字相關器是一個運算量相當大的復雜邏輯器件。

以上兩個問題使得UART接收器的邏輯結構非常龐大,并將耗用很大的邏輯資源。而在大多數嵌入式系統應用中,UART通常只是控制信息的一個接口,如果設計出來的UART的IP本身就占用了大量的邏輯資源,則使用者肯定不能接受,且這樣的UART的IP核也毫無價值。所以,要使得這種高性能的UART能在實際工程中應用,就必須優化UART的邏輯設計,減少耗用的資源。下面將以現場可編程邏輯門陣列FPGA(Field Programmable Gate Array)為設計平臺,根據UART接收器中同步模塊和數字相關器的結構特點以及FPGA的結構特點,對邏輯設計進行優化。

2.1 同步模塊的設計優化

UART的同步模塊主要檢測Sync位并得到判決信號。理想情況下,如果在一個碼元內有N次采樣,則當N次采樣的結果都為0時,表明檢測到一個Sync 位,而且此時就是數字相關器的最佳判決時刻(如圖7)。可是由于信號的邊沿抖動或是隨機脈沖干擾,N次采樣的結果通常無法達到同時為0的理想情況,如果以 N作為檢測同步的門限,則可能檢測不到Sync位,造成漏同步。

評論