高速數(shù)據(jù)采集系統(tǒng)中的存儲與傳輸控制邏輯設計

● 讀寫數(shù)據(jù)的設計

本文引用地址:http://www.czjhyjcfj.com/article/83041.htm在設計好采集數(shù)據(jù)的地址發(fā)生單元后,接下來就是配合時序進行讀寫操作。

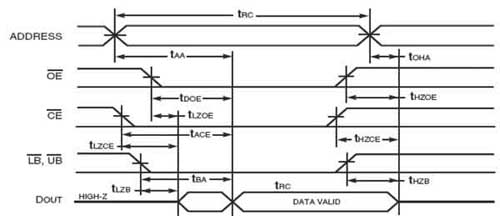

圖4是RAM的讀操作時序圖,從圖中可以看出,當指定待操作的地址后,設置芯片使能信號OE和片選使能信號CE有效,即可從數(shù)據(jù)線上讀出相應地址內(nèi)的數(shù)據(jù)。

圖4 RAM的讀數(shù)據(jù)時序圖

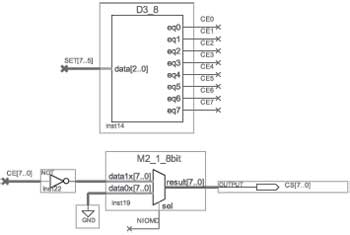

對于單片RAM的操作比較簡單,但是要將數(shù)據(jù)順序?qū)懭?片RAM中,就要求對上一片RAM寫操作完成后,系統(tǒng)能夠設置下一個待操作的RAM 有效,128位數(shù)據(jù)線分別對應8片RAM的數(shù)據(jù)線,由于地址線和讀寫使能線公用,則需要分別設置每個RAM的片選,以區(qū)別當前操作是針對哪一個RAM。片 選信號可以由譯碼器產(chǎn)生。讀操作時設置相應RAM的片選有效,即可讀出存儲的數(shù)據(jù),而進行寫操作時,則可以設置所有的RAM片選有效,將采集到的數(shù)據(jù)同時 并行的寫入8片RAM中。根據(jù)這些描述,片選信號的設計如圖5所示。NIOMD為操作的狀態(tài)信號,說明當前的操作是讀狀態(tài)或是寫狀態(tài),讀數(shù)據(jù)情況下設置為 1,片選信號分別有效,寫數(shù)據(jù)情況下設置為0,所有RAM均處于片選有效狀態(tài)下,可以同時寫入數(shù)據(jù)。這樣的設計也是為了配合系統(tǒng)的需求,一般的,讀取數(shù)據(jù) 的速度相對于寫數(shù)據(jù)來說還是要快一些的。

圖5 RAM片選使能信號設計

仿真驗證

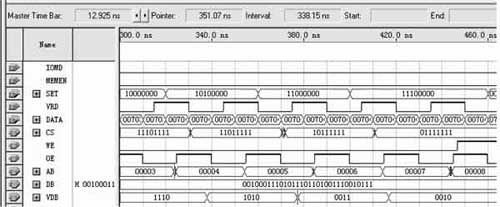

將上述設計方案整合后,配合其他控制信號的設計,就完成了數(shù)據(jù)采集系統(tǒng)數(shù)據(jù)存儲功能的設計。在QuartusII軟件中對上述設計進行波形 仿真,可以看到設置SET值及相應的狀態(tài)控制信號,則在VDB端就可以按照CS指示的相應的RAM芯片中順序讀出預先存入的數(shù)據(jù)。按照圖中所示的狀態(tài)寄存 器設置,讀取深度設置寄存器設置為最小值SET[4...1]=000,即只讀每片RAM的首個存儲數(shù)據(jù),則地址發(fā)生器的最高值為8,從圖中可以看到當?shù)?址發(fā)生器輸出值增加到8時,WE跳變?yōu)楦唠娖剑琑AM的讀使能無效。由于AB[3]=1,使得CNTEN=1,地址發(fā)生器的計數(shù)時鐘使能無效,計數(shù)器停止 計數(shù),完成一輪數(shù)據(jù)的讀取操作。讀數(shù)據(jù)仿真驗證結(jié)果如圖6所示。

圖6 讀數(shù)據(jù)仿真驗證

在圖6中,對于當前數(shù)據(jù)線上的數(shù)據(jù)串DB=0010,0011,1010,1110,1101,0011,1001,0111,片選信號 CS低電平有效,當CS=11011111時,即選中按順序由低位到高位計算的第6片RAM,此時對應的在VDB上讀出的數(shù)據(jù)應該為DB的第6個數(shù)據(jù)值, 即為1010。從波形方針圖上得到驗證。

結(jié)語

利用FPGA的內(nèi)部資源,設計靈活的邏輯控制,完成高速大容量數(shù)據(jù)采集的存儲和傳輸設計,本文提出的設計方案可以在選用低成本、操作簡單的 靜態(tài)RAM組的情況下,實現(xiàn)實時大容量數(shù)據(jù)存儲需求的一種設計方法,并在EDA軟件中進行了仿真驗證,成功地應用在1GS/s數(shù)據(jù)采集模塊中。

評論