TTL邏輯門電路

1.組成結構

TTL電路是晶體管-晶體管邏輯電路的英文字頭縮寫。它由NPN或PNP型晶體管組成,圖1是典型的TTL中速與非門電路。由于電路中載流子有電子和空穴兩種極性,因而是一種雙極型晶體管集成電路。

圖1 典型的TTL中速與非門電路

TTL電路有好幾種,其中速度最高的是STTL,即肖特基TTL電路,其平均傳輸時間約3ns,比標準型TTL約快6~7倍;功耗最低的是LSTTL,其功耗不到標準型TTL的十分之一。TTL電路與其他雙極型電路相比,在性能、價格上可謂物美價廉,已基本上取代了RTL(電阻-晶體管)電路和DTL(二極管-晶體管)電路,只是在超高速環路中仍要用ECL(發射極耦合)電路。

2.制造工藝

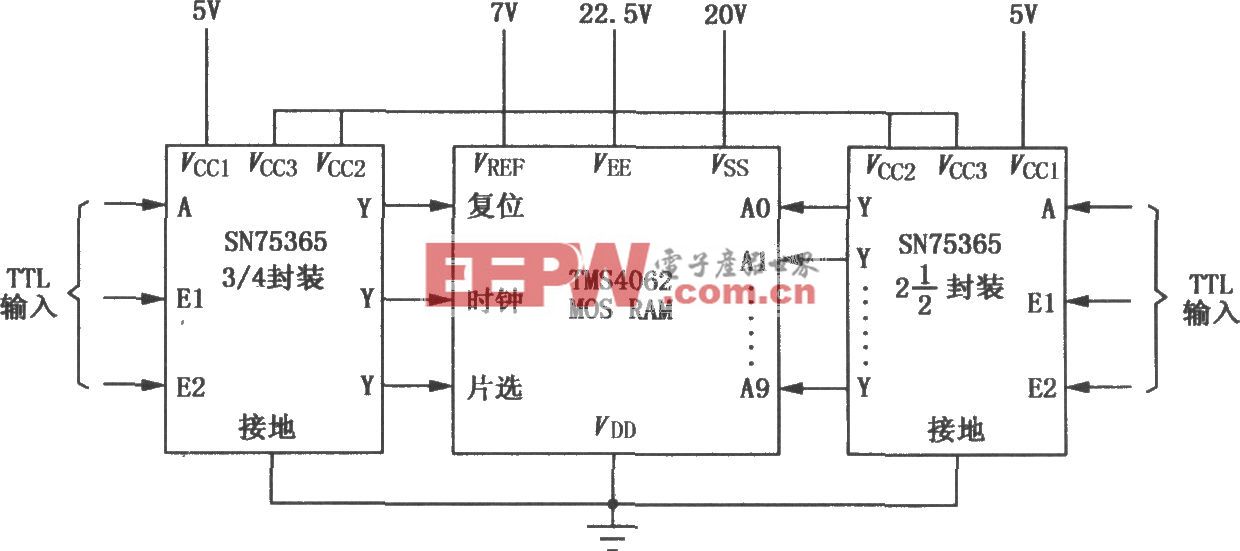

雙極型集成電路是在平面晶體管基礎上發展起來的,它的基本工藝仍然是平面工藝。但由于電路中除有晶體管外,還要集成二極管、電阻、電容等元器件,因而在制造過程中首先要把各種元器件做在一塊基片上,并使它們相互絕緣,最后再按要求將它們連成電路。從制造工藝上看,它與平面晶體管的不同,僅是增加了隔離工藝和埋層工藝。圖2是經過六次光刻、四次擴散和四次氧化制成的雙極型集成電路芯片結構,工藝較復雜。

圖2 六次光刻、四次擴散、氧化制成的雙極型集成電路芯片結構{{分頁}}

3.電路特點

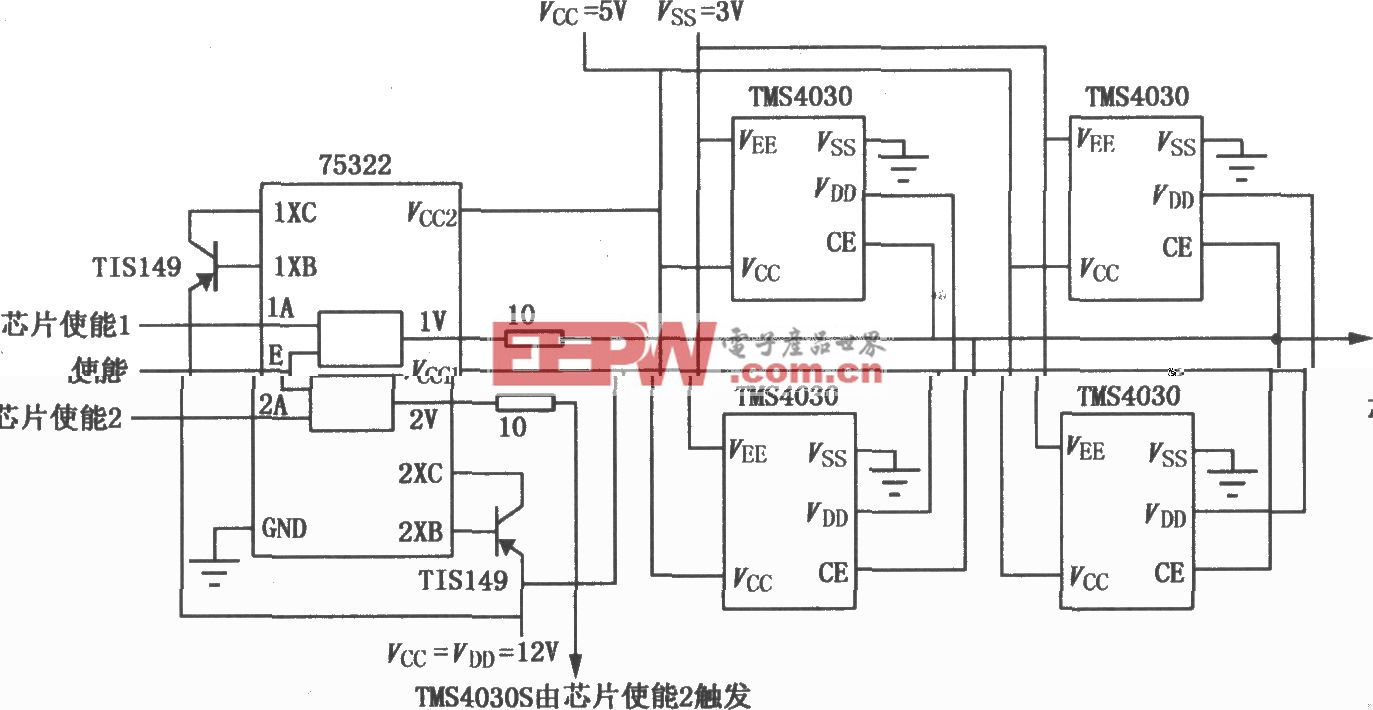

表1列出了國產TTL和各種MOS電路的四個主要參數,以便于比較。

表1 國產TTL和MOS電路主要參數

由圖3曲線可見,TTL比CMOS電路功耗大,但隨頻率提高其功耗所增無幾。

圖3 TTL與CMOS兩種電路的動態功耗電流曲線

抗干擾能力又稱噪聲容限,它表示電路保持穩定工作所能抗拒外來干擾和本身噪聲的能力,可用圖4電壓傳輸特性來說明。{{分頁}}

圖4 說明抗干擾能力的電壓傳輸特性曲線

在圖4曲線中,ViL為本級門最大輸入低電平,Vg為關門電平,Vk為開門電平,ViH為最低輸入高電平。顯然,要保持輸出高電平,干擾電壓不應超過:

![]()

式中 VNL——下限抗干擾電平。

TTL的VNL約為0.7V,而要保持輸出低電平,干擾電壓就不應超過:

![]()

式中VNH——上限抗干擾電平。

TTL的VNH約為1.5V。圖4是在電源電壓為5V時的典型曲線。

電路相關文章:電路分析基礎

pic相關文章:pic是什么

晶體管相關文章:晶體管工作原理

晶體管相關文章:晶體管原理

評論