為什么會有這么多電平標準?

電平標準的多樣性主要源于以下幾個原因:

本文引用地址:http://www.czjhyjcfj.com/article/202408/461609.htm歷史和兼容性: 不同國家和地區在不同歷史時期制定了各自的電平標準,這些標準反映了當時的技術水平和需求。隨著時間的推移,為了保持兼容性和延續性,許多舊的標準被保留下來并與新的標準共存。

應用需求: 不同的應用場景對電平有不同的要求。例如,工業控制系統、音頻設備、通信系統和計算機網絡對信號電平的要求各不相同,導致了各種專門化的電平標準的出現。

技術限制: 不同的技術在實現過程中有其自身的限制和最佳操作條件。例如,早期的電子設備和現代數字設備對電平的要求和處理能力差別很大,這導致了不同的電平標準。

標準化組織: 世界上存在多個標準化組織,如國際電工委員會(IEC)、國際標準化組織(ISO)、美國國家標準學會(ANSI)等,它們根據各自的區域和行業需求制定標準。這些組織有時會制定不同的電平標準,以滿足特定地區或行業的需求。

安全性和可靠性: 不同的應用對安全性和可靠性的要求不同。例如,電力系統需要非常嚴格的電平標準來保證安全,而消費電子產品可能更注重成本和易用性,因此在電平標準上會有所不同。

信號速率和半導體工藝的發展: 隨著信號處理和傳輸速率的不斷提高,半導體工藝也在不斷進步。這種進步導致了信號擺幅(即電壓擺幅)的不斷減小,以適應更高的速率和更小的工藝節點。例如,在現代高速內存接口如DDR(雙倍數據速率)技術中,電壓標準已經從最早的DDR的2.5V降到DDR4的1.2V,甚至更低的DDR5的1.1V。這種變化主要有以下幾個原因:

邏輯電平的一些概念

要了解邏輯電平的內容,首先要知道以下幾個概念的含義:

1:輸入高電平(VIH):保證邏輯門的輸入為高電平時所允許的最小輸入高電平,當輸入電平高于 VIH 時,則認為輸入電平為高電平。

2:輸入低電平(VIL):保證邏輯門的輸入為低電平時所允許的最大輸入低電平,當輸入電平低于 VIL 時,則認為輸入電平為低電平。

3:輸出高電平(VOH):保證邏輯門的輸出為高電平時的輸出電平的最小值,邏輯門的輸出為高電平時的電平值都必須大于此 VOH。

4:輸出低電平(VOL):保證邏輯門的輸出為低電平時的輸出電平的最大值,邏輯門的輸出為低電平時的電平值都必須小于此 VOL。

5:閾值電平(VT):數字電路芯片都存在一個閾值電平,就是電路剛剛勉強能翻轉時的電平。它是一個界于 VIL、VIH 之間的電壓值,對于 CMOS 電路的閾值電平,基本上是二分之一的電源電壓值,但要保證穩定的輸出,則必須要求輸入高電平> VIH,輸入低電平<VIL,而如果輸入電平在閾值上下,也就是 VIL~VIH 這個區域,電路的輸出會處于不穩定狀態。

對于一般的邏輯電平,以上參數的關系如下:

VOH > VIH > VT > VIL > VOL。

6:IOH:邏輯門輸出為高電平時的負載電流(為拉電流)。

7:IOL:邏輯門輸出為低電平時的負載電流(為灌電流)。

8:IIH:邏輯門輸入為高電平時的電流(為灌電流)。

9:IIL:邏輯門輸入為低電平時的電流(為拉電流)。

扇出能力也就是輸出驅動能力,通常用驅動同類器件的數量來衡量。

TTL:扇出能力一般在 10 左右。

CMOS:靜態時扇出能力達 1000 以上,但 CMOS 的交流(動態)扇出能力沒有這樣高,要根據工作頻率和負載電容來考慮決定。

限制因素是輸入信號上升時間:本身輸出

電阻和下級輸入電容形成積分電路影響輸入信號的上升時間(輸入信號從低電平上升到VIH min 所需時間),實際電路當中,盡量使被驅動輸入端限制在 10 以內。

ECL:由于 ECL 的工作速度高,考慮到負載電容的影響, ECL 的扇出一般限制在10 以內。

門電路輸出極在集成單元內不接負載電阻而直接引出作為輸出端,這種形式的門稱為開路門。開路的 TTL、 CMOS、 ECL 門分別稱為集電極開路( OC)、漏極開路

( OD)、發射極開路( OE),使用時應審查是否接上拉電阻( OC、 OD 門)或下拉電阻

( OE 門),以及電阻阻值是否合適。對于集電極開路( OC)門,其上拉電阻阻值 RL 應

滿足下面條件:

( 1):RL < ( VCC-VOH) /( n*IOH+m*IIH)

( 2):RL > ( VCC-VOL) /( IOL+m*IIL)

其中 n:線與的開路門數;m:被驅動的輸入端數。

1.2:常用的邏輯電平

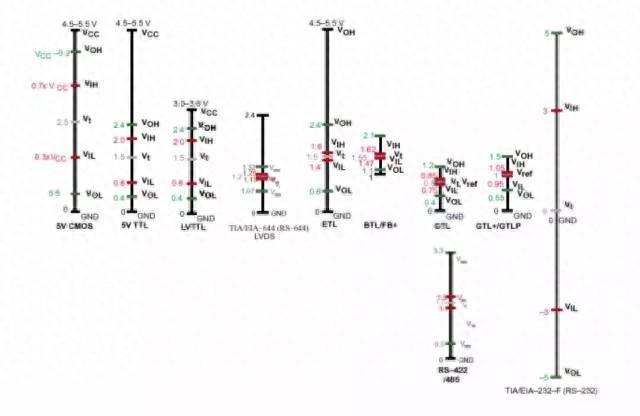

邏輯電平:有 TTL、 CMOS、 ECL、 PECL、 GTL;RS232、 RS422、 LVDS 等。

其中 TTL 和 CMOS 的邏輯電平按典型電壓可分為四類: 5V 系列( 5V TTL 和 5VCMOS)、 3.3V 系列, 2.5V 系列和 1.8V 系列。

5V TTL 和 5V CMOS 邏輯電平是通用的邏輯電平。

3.3V 及以下的邏輯電平被稱為低電壓邏輯電平,常用的為 LVTTL 電平。低電壓的邏輯電平還有 2.5V 和 1.8V 兩種。

ECL/PECL 和 LVDS 是差分輸入輸出。

RS-422/485 和 RS-232 是串口的接口標準, RS-422/485 是差分輸入輸出, RS-232是單端輸入輸。

以下是一些常見的邏輯電平標準及其相關特性:

TTL (Transistor-Transistor Logic):

邏輯低(Low):0V - 0.8V

邏輯高(High):2V - 5V

電壓范圍:

供電電壓: 通常為5V

特點: 廣泛用于早期數字電路,易于使用,但功耗相對較高。

CMOS (Complementary Metal-Oxide-Semiconductor):

邏輯低(Low):0V - 1/3 Vcc

邏輯高(High):2/3 Vcc - Vcc

電壓范圍:

供電電壓: 3.3V、5V,現代設備中也有1.8V、1.2V等

特點: 功耗低,輸入阻抗高,適用于低功耗設計。

LVTTL (Low Voltage TTL):

邏輯低(Low):0V - 0.4V

邏輯高(High):2V - 3.3V

電壓范圍:

供電電壓: 3.3V

特點: TTL的低電壓版本,功耗較低。

LVCMOS (Low Voltage CMOS):

邏輯低(Low):0V - 0.2 Vcc

邏輯高(High):0.8 Vcc - Vcc

電壓范圍:

供電電壓: 1.8V、2.5V、3.3V等

特點: 更低功耗,適用于現代低電壓應用。

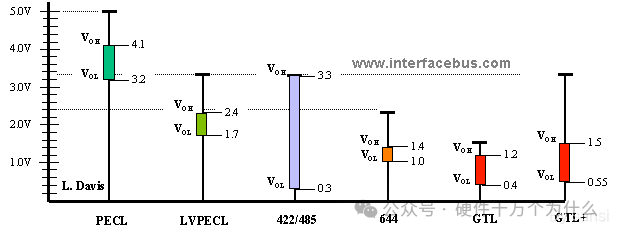

ECL (Emitter-Coupled Logic):

邏輯低(Low):-1.8V

邏輯高(High):-0.8V

電壓范圍:

供電電壓: -5.2V

特點: 非常高的速度,但功耗較大,多用于高速應用。

PECL (Positive Emitter-Coupled Logic):

邏輯低(Low):Vcc - 1.7V

邏輯高(High):Vcc - 1.0V

電壓范圍:

供電電壓: +5V或+3.3V

特點: ECL的正電源版本,高速,較高功耗。

LVDS (Low-Voltage Differential Signaling):

邏輯低(Low):電壓差 < 0V

邏輯高(High):電壓差 > 0V

電壓范圍:

供電電壓: 3.3V,1.8V等

特點: 差分信號,低電壓擺幅,低功耗,高速,抗干擾能力強。P

PCIe(Peripheral Component Interconnect Express)是一種高速串行計算機擴展總線標準,廣泛用于計算機和服務器中連接外圍設備。PCIe使用了以下幾種電平標準:

LVDS(Low-Voltage Differential Signaling):

電平標準:PCIe采用LVDS來傳輸高速數據。LVDS使用差分信號來減少電磁干擾(EMI)和串擾,從而提高數據傳輸的可靠性。

電壓范圍:差分電壓擺幅通常在250mV到450mV之間,這使得信號更加穩定和抗干擾。

CMOS(Complementary Metal-Oxide-Semiconductor):

電平標準:PCIe接口的控制信號和管理信號通常采用CMOS電平標準。

電壓范圍:這些信號的電壓范圍通常為1.2V、1.8V或3.3V,具體取決于使用的CMOS工藝節點。

HSTL (High-Speed Transceiver Logic):

邏輯低(Low):0V - 0.35V

邏輯高(High):0.65V - Vcc

電壓范圍:

供電電壓: 1.5V、1.8V等

特點: 用于高速數據傳輸,適合于DDR存儲器接口。

SSTL (Stub Series Terminated Logic):

邏輯低(Low):0V - 0.2Vcc

邏輯高(High):0.8Vcc - Vcc

電壓范圍:

供電電壓: 1.8V、2.5V、3.3V等

特點: 用于高速存儲器,如DDR SDRAM。

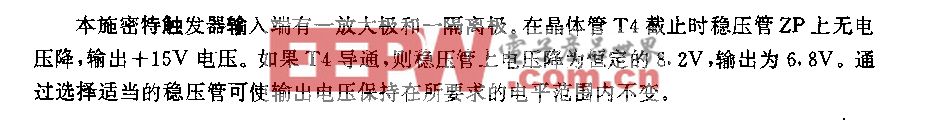

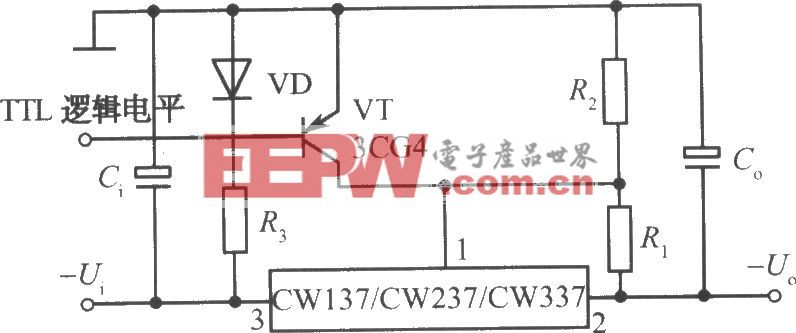

1.3開路門

門電路輸出極在集成單元內不接負載電阻而直接引出作為輸出端,這種形式的門稱為開路門。開路的TTL、CMOS、ECL門分別稱為集電極開路(OC)、漏極開路(OD)、發射極開路(OE),使用時應審查是否接上拉電阻(OC、OD門)或下拉電阻(OE門),以及電阻阻值是否合適。對于集電極開路(OC)門,其上拉電阻阻值RL應滿足下面條件:

(1):RL < (VCC-Voh)/(n*Ioh+m*Iih) 拉電流盡可能大

(2):RL > (VCC-Vol) /(Iol+m*Iil) 灌電流盡可能小

其中n:線與的開路門數;m:被驅動的輸入端數。

評論