改善分數分頻鎖相環合成器中的整數邊界雜散狀況

您曾設計過具有分數頻率合成器的鎖相環(PLL)嗎?這種合成器在整數通道上看起來很棒,但在只稍微偏離這些整數通道的頻率點上雜散就會變得高很多,是吧?如果是這樣的話,您就已經遇到過整數邊界雜散現象了 —— 該現象發生在載波的偏移距離等于到最近整數通道的距離時。

本文引用地址:http://www.czjhyjcfj.com/article/281870.htm例如,若是鑒相器頻率為100MHz,輸出頻率為2001MHz,那么整數邊界雜散將為1MHz的偏移量。在這種情況下,1MHz還是可以容忍的。但當偏移量變得過小,卻仍為非零值時,分數雜散情況會更加嚴重。

采用可編程輸入倍頻法來減少整數邊界雜散

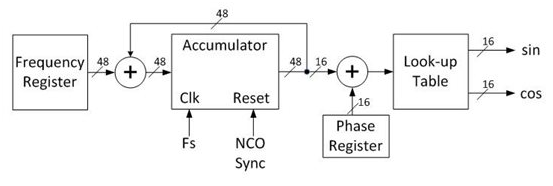

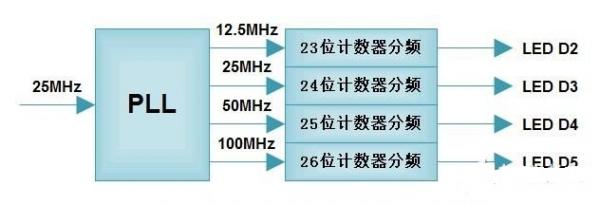

可編程倍頻器的理念是讓鑒相器頻率發生位移,這樣壓控振蕩器(VCO)頻率就能遠離整數邊界。考慮一下用20MHz的輸入頻率生成540.01MHz的輸出頻率,如圖1所示。該器件具有一個輸出分頻器(在VCO之后),但輸出頻率和VCO頻率都接近20MHz的整數倍。這種設置將迫使任何PLL產生分數雜散。

圖1:整數邊界雜散示例

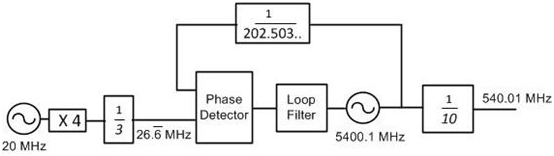

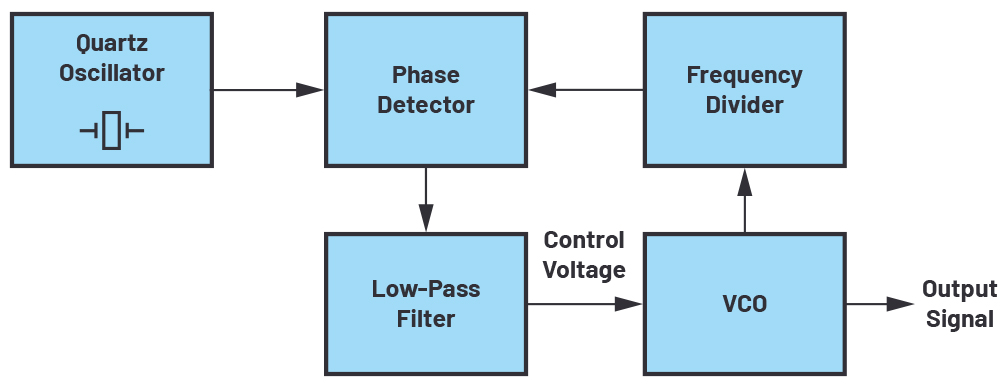

如果該器件具有一個可編程輸入倍頻器,那么圖2中所示的配置就是可行的。

圖2:用可編程倍頻器來避開整數邊界

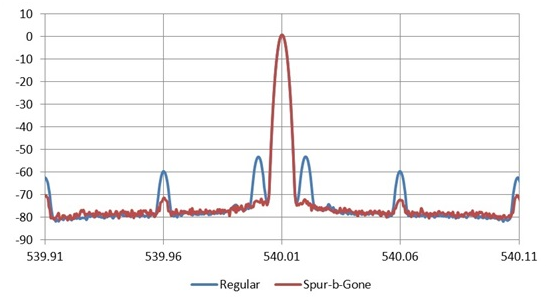

圖3展示了內部倍頻器的神奇效果。當然,整數邊界雜散有多種發生機制,很難完全消除它們。但這種方法可減少整數邊界雜散及其產生的其它雜散。

圖3中的“雜散消失”路徑展示了使用該可編程倍頻器的效果。100kHz頻率下的整數邊界雜散大約減少了9dB,同時還大大減少了50kHz和10kHz頻率下的其它雜散。

圖3:使用和不用可編程倍頻器時的雜散比較

本文中列舉的示例都采用了TI的LMX2571合成器 —— 該器件包含一個無需外部組件的可編程倍頻器。此外,這款合成器還具有39mA的電流消耗、-231dBc/Hz的PLL相位噪聲優值以及10-1344MHz的連續輸出頻率范圍。它能支持陸地移動無線電、軟件定義無線電和無線麥克風等應用。

鑒相器相關文章:鑒相器原理 鎖相環相關文章:鎖相環原理

評論