小梅哥和你一起深入學習FPGA之DAC驅動

本實驗中,我們使用FPGA來驅動了一片DAC芯片TLC5620,該芯片的特性如下所示:

本文引用地址:http://www.czjhyjcfj.com/article/278347.htmTLC5620特性:

4路8位電壓輸出;

單電源5V供電;

串行接口;

參考電壓輸入高阻;

可編程的1次或2次輸出范圍;

同時更新的能力;

內部自帶上電復位功能;

低功耗;

半緩沖輸出。

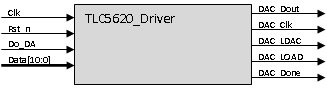

小梅哥設計的該芯片的驅動模塊的接口如下所示:

各個端口定義如下:

以下是代碼片段:

input Clk;

input Rst_n;

input Do_DA; /*使能單次轉換*/

input [10:0]Data;/*{Addr1,Addr0,Range,Data_bit[7:0]}*/

output reg DAC_Dout; /*DAC數據線*/

output reg DAC_Clk; /*DAC時鐘線,最高速度1M*/

output reg DAC_LDAC; /**/

output reg DAC_LOAD; /**/

output reg DA_Done; /*單次轉換完成標志信號*/

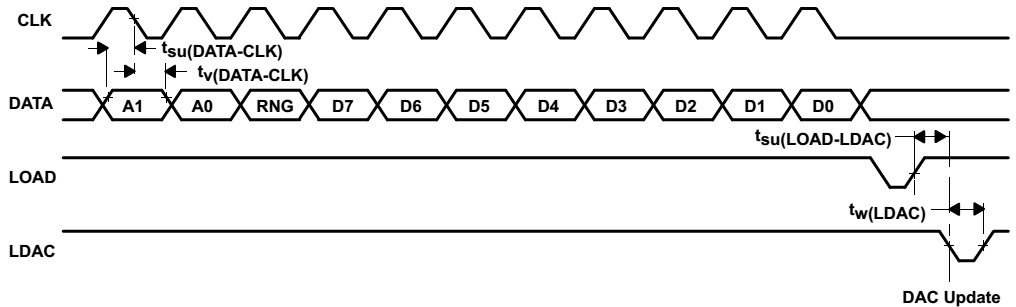

該芯片提供了類似于SPI的數字接口,因此,我們只需要使用該接口與芯片進行通信,再配合LOAD和LDAC兩個控制線,即可實現對該DAC芯片的控制。TLC5620一次轉換的操作時序如下:

圖1 TLC5620單次轉換時序圖

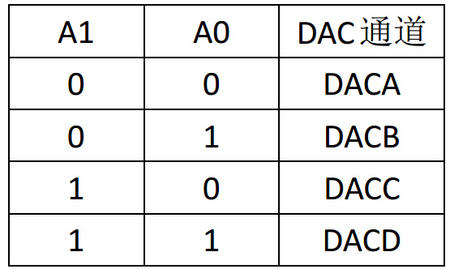

TLC5620每次寫入的數據為11位,其中前兩位為DAC選擇位A1、A0,通過不同的組合可以選擇不同通道的DAC,具體分配為:

表1 DAC通道選擇位與對應通道關系

第三位是電壓輸出增益位,0代表不變,1代表兩倍,當設定參考電壓為2.5V時,取這一位為1就可以得到最高5V的輸出電壓。后面8位是數據位,其中第四位是數據的最高位。對于TLC5620的輸出電壓公式是:

VO=VREF ×CODE/256×(1+RNG)

VREF是參考電壓,CODE是待轉換的8位二進制代碼,RNG是增益倍數。

寫入數據時,首先LOAD和LDAC寫高電平,這樣在CLK的每個下降沿寫入的每位數據被鎖存到DATA端,當11位數據傳送完畢后,拉低LOAD,芯片根據前兩位數據,判斷是哪一路DAC通道,然后將8位數據移入相應的通道,進行DA轉換,這時拉低LDAC,再拉高LDAC,就可以再下次轉化之前,保持此次的模擬輸出。

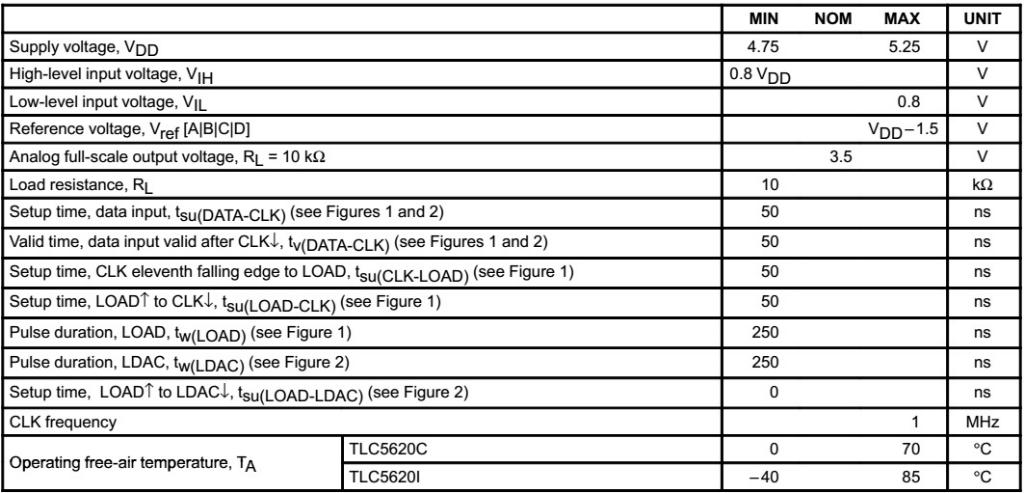

TLC5620正常工作時的具體電壓和時間參數如下表所示,通過該表,可知該芯片串行數字接口的時鐘信號(CLK)最高為1MHz。該參數將作為我們采用FPGA產生TLC5620數字接口時鐘的依據。同時,還有輸入數據建立時間tsu(data-clk)為50ns,即,FPGA數據送出,到能夠被TLC5620正常讀取,至少需要50ns,因此FPGA單位數據輸出保持時間不得少于50ns。tv(data-clk)為時鐘下降沿到來后多久時間數據線上的數據才能被芯片內部采集,該時間確定了,時鐘下降沿出現多久后,數據線上的數據可以被更新。tsu(LOAD-LDAC)為LOAD的上升沿到LDAC下降沿的建立時間,這里最小為0ns,因此忽略,即兩者同時發生即可。tw(LDAC)為LDAC低電平所需的最短時間,為250ns。

表2 TLC5620關鍵參數

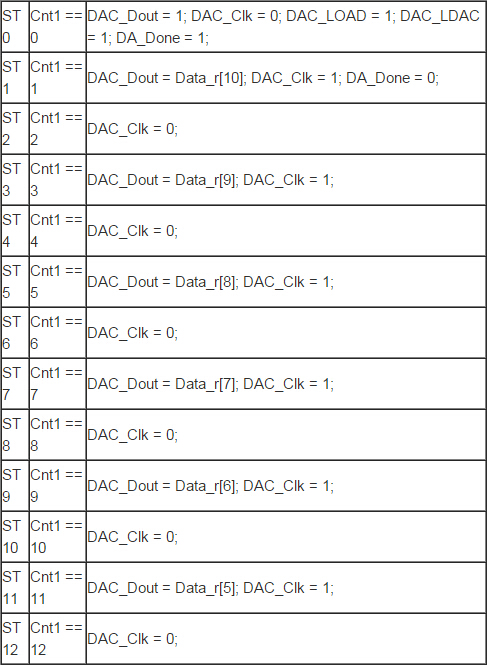

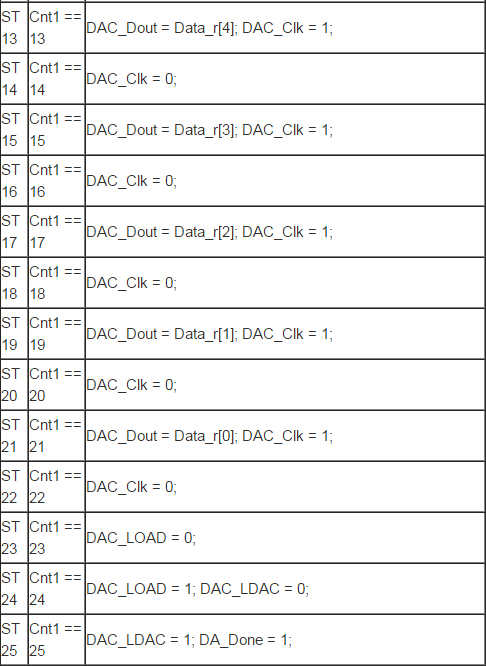

通過對TLC5620一次完整轉換的時序進行分析,列出以下序列機對應的序列點:該序列機總共包含26個點,其中,當Cnt1=0(ST0)時,為空閑態,ST1—ST22為數據發送狀態,ST23時拉低LOAD,即將數據加載入對應通道的DAC中,ST24時釋放LOAD,同時拉低LDAC,以產生LDAC的下降沿,將對應通道的模擬輸出保持住。ST25拉高LDAC,完成一次轉換。

表3 TLC5620單次轉換控制序列機

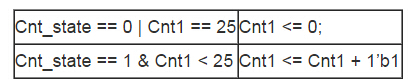

序列機的計數器計數條件如下

表4 TLC5620序列機計數器計數條件

fpga相關文章:fpga是什么

路由器相關文章:路由器工作原理

路由器相關文章:路由器工作原理

塵埃粒子計數器相關文章:塵埃粒子計數器原理

評論