用Xilinx Vivado HLS實現(xiàn)浮點復(fù)數(shù)QRD矩陣分解

在數(shù)字信號處理領(lǐng)域,如自適應(yīng)濾波、DPD系數(shù)計算、MIMO Decoder 等,常常需要矩陣解方程運算以獲得其系數(shù),因此需對矩陣進(jìn)行求逆運算。然而,由于直接對矩陣求逆會導(dǎo)致龐大的運算量,所以在實際工程中往往需要先將矩陣分解成幾個特殊矩陣(正規(guī)正交矩陣或上、下三角矩陣以求其逆矩陣需要更小的運算量)的乘積。目前,QRD矩陣分解法是求一般矩陣全部特征值的最有效且廣泛應(yīng)用的方法之一。它是將矩陣分解成一個正規(guī)正交矩陣Q與上三角形矩陣R,稱為QRD矩陣分解。

本文引用地址:http://www.czjhyjcfj.com/article/273080.htm由于浮點具有更大的數(shù)據(jù)動態(tài)范圍,所以在眾多多算法中具有只需要一種數(shù)據(jù)類型的優(yōu)勢,所以很多QRD矩陣分解是基于浮點數(shù)據(jù)類型的。不過在通信應(yīng)用中,更多的場景還是復(fù)數(shù)類型。因此,隨著通信技術(shù)的日益發(fā)展,算法的復(fù)雜度越來越高,QRD矩陣的維度也越來越大。如果是用傳統(tǒng)的手寫RTL,浮點復(fù)數(shù)超大維度QRD矩陣分解的FPGA實現(xiàn)將變得非常復(fù)雜,需要很長的時間來編寫RTL代碼、仿真和進(jìn)行驗證等工作,使得開發(fā)效率不是很高。

本文將介紹如何使用Xilinx Vivado HLS(Vivado 高層次綜合)工具實現(xiàn)浮點復(fù)數(shù)QRD矩陣分解并提升開發(fā)效率。使用Vivado HLS可以快速、高效地基于FPGA實現(xiàn)各種矩陣分解算法,降低開發(fā)者對算法FPGA的實現(xiàn)難度。其中包括:

- 使用Vivado HLS開發(fā)效率比手寫RTL實現(xiàn)快5-10倍,而實現(xiàn)的FPGA資源效率與手寫RTL接近

- 由于C/C++仿真驗證比傳統(tǒng)FPGA RTL要快100倍,Vivado HLS實現(xiàn)可以大大縮短用戶的代碼開發(fā)時間和仿真驗證時間,從而大幅提高生產(chǎn)效率。

1. Vivado HLS工具介紹

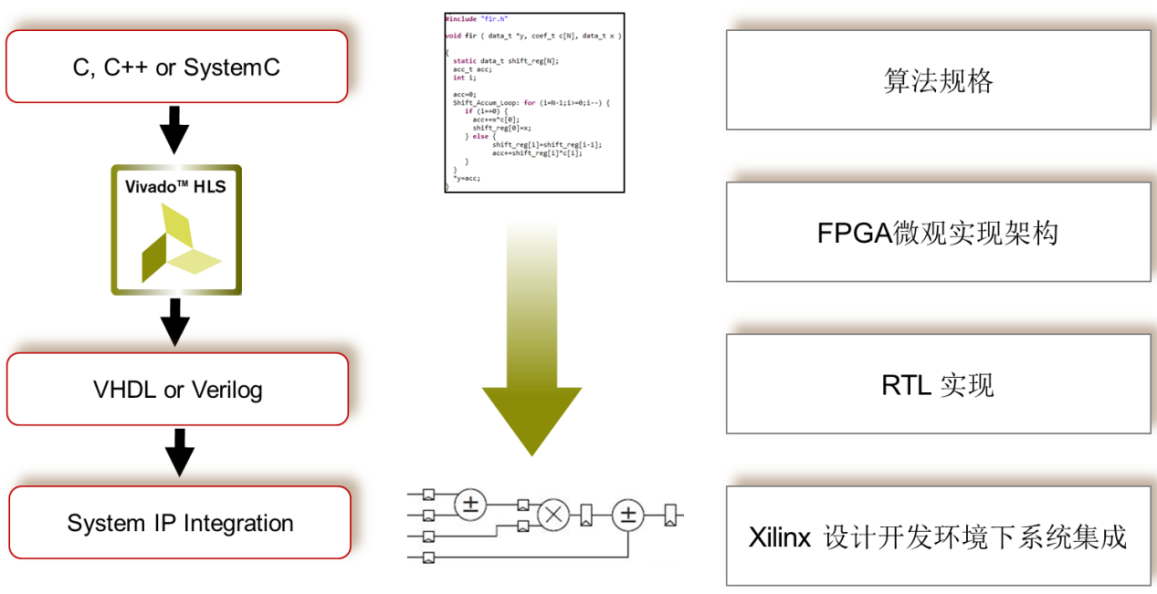

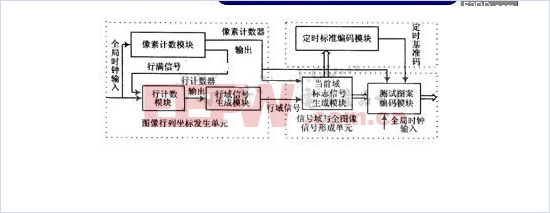

Vivado HLS 是Xilinx公司2010 年收購 AutoESL 以后重新打造的高層次綜合工具,它可以讓用戶通過添加適當(dāng)?shù)膁irectives(制導(dǎo)語句) 和 constrains(約束), 將其C/C++/System C代碼直接轉(zhuǎn)換成 FPGA RTL( Verilog, VHDL, System C )代碼。讓用戶可以在算法開發(fā)環(huán)境而非通常的硬件開發(fā)環(huán)境中只需專注于算法規(guī)格和算法的 C 實現(xiàn),Vivado HLS 工具會自動考慮 FPGA 微觀實現(xiàn)架構(gòu),并可生成可綜合的FPGA RTL代碼。如圖1所示。

圖1 Vivado HLS設(shè)計介紹

Vivado HLS FPGA設(shè)計流程:

- 首先用 C/C++/System C 將算法實現(xiàn),并編寫 C testbench 驗證 C 的功能,確保其功能正確;

- 然后就可以通過 Vivado HLS 工具進(jìn)行 C 綜合,將 C 轉(zhuǎn)換成 RTL;

- 接著做 C/RTL 的協(xié)同仿真(Co-simulation),以保證生成的RTL代碼功能與C的功能完全一致。

- 最后 Vivado HLS 生成的 RTL 代碼可直接用于 Xilinx 設(shè)計開發(fā)環(huán)境下做系統(tǒng)集成、仿真和生成bit文件。

圖2 Vivado HLS設(shè)計流程

2. QRD矩陣分解算法

QRD矩陣分解是將一個矩陣A分解成Q與R相乘,

其中R是個上三角矩陣, Q是個正交矩陣,

Q = 1

是Q的轉(zhuǎn)置共軛矩陣

3. QRD矩陣分解 Vivado HLS 實現(xiàn)C++代碼構(gòu)架

QRD矩陣分解C++實現(xiàn)代碼的頂層模塊是qrd_engine.cpp, 它調(diào)用cal_core.cpp(核心計算函數(shù)), coef_cal.cpp(系數(shù)計算函數(shù)),以及浮點加、減、乘、除法等子函數(shù)來實現(xiàn)。

struct cf_t {

float re;

float im;

};

void qrd_engine

(

cf_t in_u[(R_DIM+Y_DIM)/DIV_NUM][DIV_NUM],

cf_t pd_err_in,

float lamda,

float lamda_sqrt,

float diag[R_DIM],

cf_t r[R_DIM][X_DIM],

cf_t p[R_DIM]

)

{

#pragma HLS ARRAY_PARTITION variable=in_u complete dim=2

#pragma HLS ARRAY_PARTITION variable=r complete dim=2

//注:這里對數(shù)組加入完全分割directive,目的是提高數(shù)據(jù)的并行帶寬,從而獲得并行計算。

#pragma HLS RESOURCE variable=in_u core=RAM3S

//注:這里對數(shù)組加入RAM3S directive,目的是控制生成的BRAM的延遲。

for (i=0;i

{

#pragma HLS PIPELINE II =124

#pragma HLS latency max = 123

//注:這里加入II(interval是指下一個新的可以輸入QRD模塊的數(shù)據(jù)與前一個數(shù)據(jù)之間所間隔的時鐘周期數(shù))及l(fā)atency directives (延遲制導(dǎo)語句),目的是控制這個模塊在指定的延遲節(jié)拍范圍內(nèi)完成所有的計算。

coef_calc(lamda_sqrt,lamda,diag[i],pre_in_u,pd_err_in,&s_o,&s_conj_o,&lamda_sqrtxs_o,&c_o,&lamda_sqrtxc_o,&diag_out,&p_o,&pd_err);

cal_core(u_tmp, r_tmp, s_n, i, j, k, c_o, lamda_sqrtxc_o, lamda_sqrtxs_o, s_conj_o, &in_u_w2, &r[i][r_addr]);

}

}

void coef_calc

(

float lamda_sqrt,

float lamda,

float r_diag,

cf_t u_diag,

cf_t pd_err_in,

cf_t *s,

cf_t *s_conj,

cf_t *lamda_sqrtxs,

float *c,

float *lamda_sqrtxc,

float *diag,

cf_t *p_o,

cf_t *pd_err

)

void calc_core

(

cf_t in_u,

cf_t r,

int s_n,

int i,

unsigned char j,

unsigned char k,

float c_o,

float lamda_sqrtxc_o,

cf_t lamda_sqrtxs_o,

cf_t s_conj_o,

cf_t* u_ret,

cf_t* r_ret

)

4. QRD矩陣分解的Vivado HLS設(shè)計實現(xiàn)與優(yōu)化

4.1 C模塊劃分

Vivado HLS生成的RTL代碼在默認(rèn)情況下保留原有c代碼的層次結(jié)構(gòu)。在構(gòu)建c代碼層次時,可以采用由上至下、自下而上相結(jié)合的模塊劃分方式。

將單精度浮點基本運算如加、減、乘、除、平方根等寫成最底層的子函數(shù),以便添加directives來指導(dǎo)工具優(yōu)化方向。

float hfmult

(

float in1,

float in2

)

{

#pragma HLS PIPELINE

// 注:將hfmult函數(shù)流水化設(shè)計,以獲得更好的時序性能

#pragma HLS RESOURCE variable=return core=FMul_fulldsp latency=9

// 注:制定hfmult的延遲為9個時鐘周期,以便hfmult內(nèi)部實現(xiàn)有充分的時鐘節(jié)拍流水,特別是有足夠的時鐘節(jié)拍分配給DSP48內(nèi)部做流水處理

float out;

out = in1 * in2;

}

類似的設(shè)計方法及思路也同樣適用于浮點加,減等運算。

4.2 提高C轉(zhuǎn)換成FPGA RTL 實現(xiàn)的并行度

由于計算時間、速度的要求,往往需要提高運算的并行度,需要對qrd_engine中in_u及r數(shù)組(HLS綜合成FPGA的BRAM或分布式RAM)加數(shù)組分割directive,這樣數(shù)據(jù)才可以并行進(jìn)入后面的并行處理單元。

#pragma HLS ARRAY_PARTITION variable=in_u complete dim=2

#pragma HLS ARRAY_PARTITION variable=r complete dim=2

4.3 對數(shù)組memory地址讀寫設(shè)計優(yōu)化

C語言中的數(shù)組通常會被綜合成FPGA的存儲memory,這樣就會有地址的讀寫。但為了達(dá)到更好的時序性能,可以盡量減少對memory的讀寫,從而簡化所生成RTL代碼中的mux。

寫法1,定義成,in_u[i/DIV_UNM][i%DIV_NUM],對下面的運算,將產(chǎn)生兩次memory讀寫。

calc_coef(lamda_sqrt, in_u[i/DIV_UNM][i%DIV_NUM], …);

for(j=0; j

for(k=0; k

{

in_u_read = in_u[u_addr][k];

}

寫法2,定義成變量in_u_pre, 通過 if(u_addr == (i+1)/DIV_NUM && k==(i+1)%DIV_NUM)判斷來實現(xiàn)同樣的功能,這樣只需要一次memory讀寫,從而獲得更好的II性能,當(dāng)然也提升了時序性能。

calc_coef(lamda_sqrt, in_u_pre, …);

for(j=0; j

for(k=0; k

{

in_u_read = in_u[u_addr][k];

if(u_addr == (i+1)/DIV_NUM && ==(i+1)%DIV_NUM)

in_u_pre = in_u_read;

}

有時為了使in_u綜合出的RAM時序更好,也可以對in_u綜合的RAM加resource directive來控制其stage, 比如為3 stage,這樣生成的RAM, 在輸入,輸出都會打一拍register。

#pragma HLS RESOURCE variable=in_u core=RAM3S

4.4 浮點運算加法級聯(lián)與加法樹

由于浮點運算的精度與其運算的先后順序有直接關(guān)系,在Vivado HLS中,為了保證生成的RTL代碼與C中的精度一樣, Viado-HLS一般不會改變代碼中中浮點運算的順序。有時為降低浮點運算的latency,使用并行加法樹將比串行級聯(lián)加法來獲得更有效。

浮點串行加法級聯(lián),這樣寫法是有嚴(yán)格先后順序的,Vivado HLS將其生成串行實現(xiàn)的RTL代碼,其latency為35個時鐘周期。

void fp_adder_cascade (float *r, float a, float b, float c, float d)

{

#pragma HLS PIPELINE

*r = a + b + c + d;

}

如果用戶確定上面的浮點加順序調(diào)整對精度的影響在誤差范圍內(nèi), 那么可以采用并行加法樹,這樣 Vivado HLS 將其生成并行加法RTL代碼實現(xiàn),其latency為降為23個時鐘周期。

void fp_adder_tree (float *r, float a, float b, float c, float d)

{

#pragma HLS PIPELINE

float e, f;

e = a + b;

f = c + d;

*r = e + f;

}

4.5 對浮點乘法使用的DSP48的優(yōu)化

同樣我們也可以通過設(shè)置充足的latency directive給DSP48,這樣有足夠的時鐘節(jié)拍給到DSP48內(nèi)部打拍register。

如果對上述的單精度浮點乘法hfmult latency設(shè)置為3,這樣分配到每個DSP48 內(nèi)部只有2級latency, 那么綜合總合出來代碼DSP48內(nèi)部的A_reg 或 P_reg不會打一拍, 這樣將會大大降低時序性能。

derive_core fmul_der -base FMul_maxdsp -latency 3 -fixed

set_directive_resource -core fmul_der hfmult out

或者:

為了達(dá)到較好的時序性能,對上述的單精度浮點乘法hfmult latency至少設(shè)置為4,這樣分配到每個DSP48 內(nèi)部只有3級latency, 那么綜合總合出來代碼DSP48內(nèi)部的A_reg 或 P_reg都會各打一拍。

derive_core fmul_der -base FMul_maxdsp -latency 4 -fixed

set_directive_resource -core fmul_der hfmult out

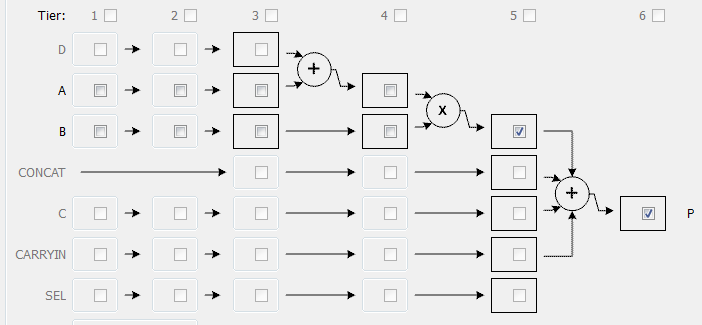

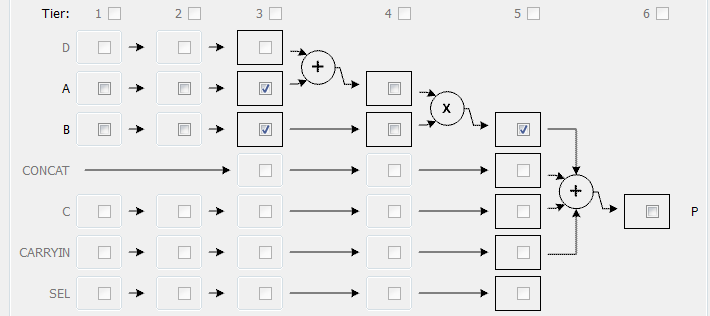

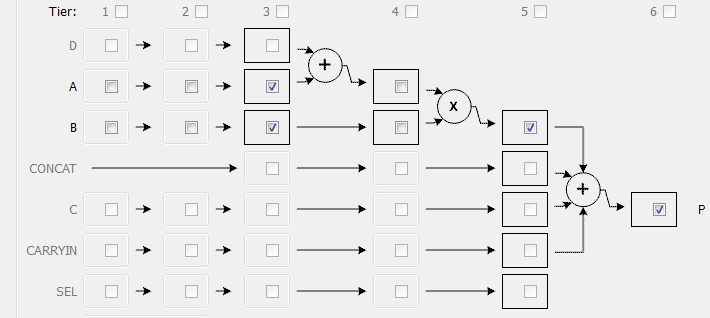

4.6 對Shifter Register的優(yōu)化

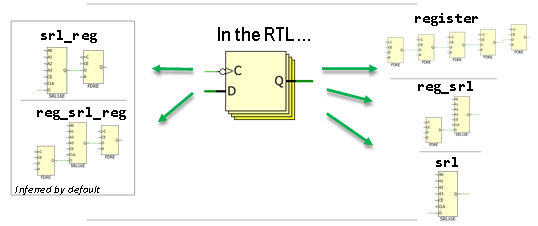

利用Vivado HLS 2014.4的Shift Register RTL Attribute,有5種類型SRL來控制不同的shifter register組合:srl, srl_reg, reg_srl, reg_srl_reg。

比如在Vivado HLS生成的RTL代碼中加(* srl_style “reg_srl_reg” *),將綜合成在SRL之前、之后分別用一個register來實現(xiàn)。如圖所示:

5. Vivado HLS QRD矩陣分解設(shè)計結(jié)果

本文中QRD矩陣分解的大小是128x128的單精度復(fù)數(shù)浮點,我們使用Xilinx

Vivado HLS 2014.4版本,將其生成的RTL在Xilinx Virtex-7 FPGA上實現(xiàn)。

5.1 延遲(latency)性能

本文所述的設(shè)計,在Xilinx Vivado HLS 2014.4中達(dá)到的延遲15237個時鐘周期。

5.2 Interval(吞吐率的倒數(shù))性能

在Xilinx Vivado HLS中,interval是指下一個新的可以輸入QRD模塊的數(shù)據(jù)與前一個數(shù)據(jù)之間所間隔的時鐘周期數(shù),也可以理解為吞吐率的倒數(shù)。這里Interval的單位是時鐘周期。

本文所述的設(shè)計,在Xilinx Vivado HLS 2014.4 中達(dá)到的Interval是15238個時鐘周期。

5.3 時序(timing)性能

使用Xilinx Vivado HLS 2014.4在Xilinx Virtex-7器件中實現(xiàn)單個128x128單精度浮點復(fù)數(shù)QRD分解模塊,時鐘頻率達(dá)到了350 MHz (2.85ns)。

5.4 處理時間性能

QRD矩陣分解的處理時間就是所用的延遲x時鐘周期,所以是:15237 x 2.85 = 43.4 uS。

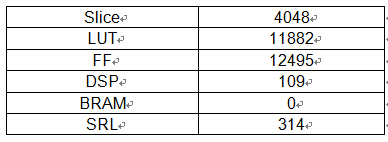

5.5 FPGA資源

將Xilinx Vivado HLS 2014.4生成的RTL代碼,在Vivado 2014.4中綜合,實現(xiàn),使用的資源如下表。這個資源使用率只占Xilinx Virtex-7 7V485T的4%,使用Vivado HLS 2014.4高效地實現(xiàn)了QRD矩陣分解。

6. 總結(jié)

使用Xilinx Vivado HLS工具,可以讓算法工程師、FPGA工程師及軟件工程師快速基于FPGA實現(xiàn)典型的數(shù)字信號處理算法。本文以浮點復(fù)數(shù)QRD矩陣分解為例,介紹了如何使用 Vivado HLS 快速、高效地基于FPGA實現(xiàn),并降低開發(fā)者對算法的FPGA實現(xiàn)難度。

Vivado HLS可以幫助設(shè)計者大幅提升生產(chǎn)力。 使用 Vivado HLS 開發(fā)效率比手寫RTL實現(xiàn)快5-10倍,其FPGA資源效率與手寫RTL接近,且C/C++仿真驗證比傳統(tǒng)FPGA RTL要快100倍。

Xilinx公司資深DSP專家王宏強(qiáng)

Xilinx公司高級FAE 徐堅鄧濤

Xilinx公司工具與方法學(xué)高級專家徐天容

c語言相關(guān)文章:c語言教程

c++相關(guān)文章:c++教程

評論