一種基于DSP的MIMO系統空時編碼盲識別方法

空時編碼(Space—Time Block Coding,STBC)是達到或接近MIMO無線信道容量的一種有效的編碼方式。空時編碼方式的盲識別是通信對抗領域需迫切研究的領域,其能夠為MIMO系統對抗技術提供基礎和技術支撐,具有重要的研究價值。

本文引用地址:http://www.czjhyjcfj.com/article/272884.htm時滯相關算法是根據不同空時編碼的相關矩陣在不同時延統計下的差異性,采用逐級對比,實現對空時編碼方式的盲識別。擁有計算精度高,抗頻偏效果好等優點。文中提出一種基于ADI公司DSP芯片TigerSHARCTS201S的空時編碼盲識別方案設計和實現。

1系統硬件設計

1.1系統硬件框圖

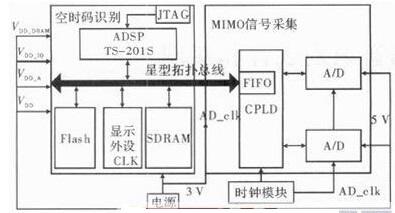

系統硬件框圖如圖1所示。由信號處理、信號采集、電源、時鐘4部分構成,信號采集由CPLD和ADC組成,負責完成A/D轉換,信號處理由TS201S芯片及其外設組成,用于存儲A/D采樣的數據,并進行空時碼盲識別運算處理。電源模塊為其他所有模塊提供正常工作所需的電壓,時鐘模塊中由晶振和倍頻芯片組成,提供系統所需時鐘。

圖1 系統硬件框圖

系統工作時,設備首先通電初始化,從Flash中載入用戶應用程序,繼而通過CPLD控制ADC進行數據采集,并利用DMA中斷方式讀取數據并進行編碼識別運算。

1.2 TigerSHARC TS201S簡介

TigerSHARC TS201S兼有ASIC和FPGA的信號處理性能和指令集處理器的高度可編程性與靈活性,適用于高性能、大存儲量的信號處理與圖像應用。

TS201S內部分為DSP核和I/O接口兩部分,通過4條總線傳輸數據、地址和控制信息。并提供完全可中斷的編程模式,支持匯編和C/C++語言編程,32/40位的浮點運算及最高64位的定點運算。在600 MHz時鐘速率下,可達到每秒48億次乘加運算。

1.3電源、時鐘和總線方案設計

TS201S和AD7864對電源的要求較高,以TS201S內核時鐘500 MHz為例,4個電源VDD、VDD_A、VDD_IO、VDD_DRAM的精度要求控制在5%以內。因此系統中的電源芯片采用了,其精度可達1%.

時鐘模塊中,晶振產生27 MHz時鐘通過倍頻芯片得到54 MHz時鐘后進入CPLD,一方面作為TS201S的系統時鐘SCLK,另一方面在CPLD內12分頻后作為AD7864的工作時鐘信號AD_CLK.為防止其對系統電源產生耦合干擾,晶振和倍頻芯片的電源與本板電源之間要用電感或磁珠進行隔離。

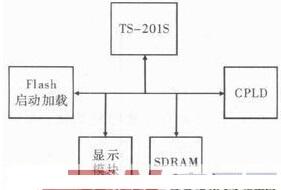

在系統總線負載較重的情況下,設計不當會限制總線只能在低頻下工作甚至無法讀取數據。由于環形結構上任一負載的變化均會影響到其他負載的工作,設計中采用了星形總線結構,如圖2所示。

圖2 星形總線結構

1.4信號采集方案設計

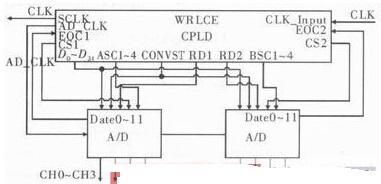

信號采集模塊由CPLD和兩片ADC組成,A/D轉換芯片采用AD公司生產的AD7864,其轉換精度12位,最高吞吐量520 ksample.s-1,轉換時間最快為1.65μs,采樣保持0.35μs,此外其單電源和低功耗特性最低可達20 Uw,其能夠滿足系統的要求,簡化硬件設計。

信號采集前,需對AD7864的一些輸入引腳進行配置,南Alterta公司的CPLD產品MAX3256完成。如圖3所示,CONVST為使能輸入引腳,置位高可控制AD7864啟動。CS為片選信號,低電平有效。RD為讀使能,低電平有效,當CS有效且RD為低,才允許AD7864輸出轉換結果,此時WR必須為高。引腳SL1~SL4是AD7864的通道選擇輸入引腳,高電平有效。H/S SEL為高時表示將通過軟件方式來選擇A/D轉換通道,反之表示硬件選擇。當轉換結束后,EOC引腳輸入低電平。

圖3 信號采集

AD7864采用分時輸出方式,采樣信號來自TS201S的定時/計數器,每次計數器滿時TMROE引腳會產生4個總線時鐘的高電平,CPLD中對此信號做反向后作為AD7864的CONVST信號,在數據傳輸中,片1占低位數據線,片2占高位數據線,分時可防止總線沖突。

1.5顯示方案設計

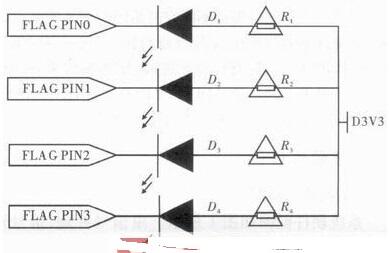

系統采用FLAG PIN外接LED做為進度顯示,DSP在執行到不同的處理進度時通過改變FLAG PIN口的電平控制對應的LED導通,以指示當前數據分析的步驟。圖4為外接LED的連接圖,每個FLAG PIN上的LED均不影響其他FLAG PIN接口,在LED后使用了一個上拉電阻接VCC.

圖4 為外接LED的連接圖

c++相關文章:c++教程

塵埃粒子計數器相關文章:塵埃粒子計數器原理 晶振相關文章:晶振原理 上拉電阻相關文章:上拉電阻原理

評論