基于SoPC的FIR濾波器設計與實現

0 引言

本文引用地址:http://www.czjhyjcfj.com/article/267759.htm數字濾波(idgital filter)是由數字乘法器、加法器和延時單元組成的一種計算方法。其功能是對輸入離散信號的數字代碼進行運算處理,以達到改變信號頻譜的目的。數字濾波器根據頻域特性可分為低通、高通、帶通和帶阻4個基本類型;根據時域特性可分為無限脈沖響應(infinite impulse response,IIR)濾波器和有限脈沖響應(finite impulse response,FIR)濾波器。FIR濾波器不存在穩定性和是否可實現的問題,容易做到線性相位,故在數據通信、圖像處理等領域廣泛應用。

目前,FIR濾波器的硬件實現有以下幾種方式:一種是使用通用數字濾波器集成電路,這種電路使用簡單,但是由于字長和階數的規格較少,不易完全滿足實際需要;雖然可采用多片擴展來滿足要求,但會增加體積和功耗,因而在實際應用中受到限制。另一種是使用DSP芯片,DSP芯片有專用的數字信號處理函數可調用,實現FIR濾波器相對簡單,但是由于程序順序執行,速度受到限制。而且,就是同一公司不同系統的DSP芯片,其編程指令也會有所不同,開發周期較長。還有一種是使用可編程邏輯器件,如FPGA(field programmable gate array),即現場可編程門陣列,有著規整的內部邏輯塊整列和豐富的連線資源,特別適合用于細粒度和高并行度結構的FIR濾波器實現,相對于串行運算主導的通用DSP芯片來說,并行性和可擴展性都更好。

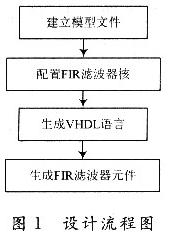

本文介紹一種基于SoPC的FIR濾波器設計方案,設計流程如圖l所示。該設計方法程序簡單,調試方便,得到的FIR濾波器精確度高。

1 FIR濾波器原理

FIR數字濾波器是一種非遞歸系統,其沖激響應總是有限長的,其系統函數可以記為:

y(n)=x(n)*h(n)

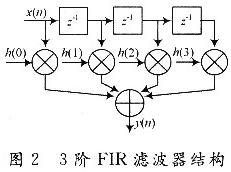

圖2顯示了一個典型的直接T型3階FIR濾波器,其輸出序列y(n)滿足下列等式:

在該FIR濾波器中,總共存在3個延時結,4個乘法單元,1個4輸入的加法器。如果采用普通的數字信號處理器(DSP)來實現,只能用串行的方式順序地執行延時、乘加操作,不可能在1個DSP處理器指令周期內完成,必須用多個指令周期來完成。但如果采用FPGA來實現,就可以采用并行結構,在1個時鐘周期內得到1個FIR濾波器的輸出。不難發現,圖2的電路結構是一種流水線結構,這種結構在硬件系統中有利于并行高速運行。

2 FIR濾波器的實現

Altera提供的FIR Complier是結合Altera FPGA器件的FIR Filter Core,DSP Builder與FIR Compiler可以緊密結合起來。DSP Builder提供了FIR Core的應用環境和仿真驗證環境。

2.1 建立模型文件

為了調用FIR IP Core,在Simulink環境中新建模型文件,放置Sigtlal Compiler模塊和FIR模塊。啟動Simulink的方法:打開Matlab,在主命令窗口直接鍵入Simulink,按回車即可。然后打開Altera DSP Builder模塊,在MegaCore FuncTIons調出fir_compiler_v7_0。

2.2 配置FIR濾波器核

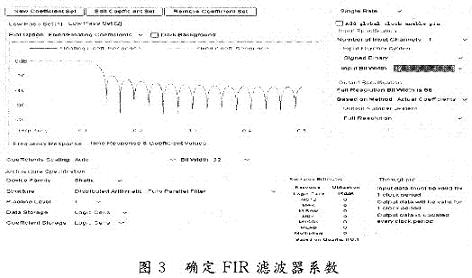

雙擊模型中的FIR模塊,在彈出來的選擇窗口中有:關于這個核(about this core)、程序說明書(documentation)、顯示元件(display symb01)、步驟1確定參數(Stepl:Parameterize)和步驟2生成(Step2:Generate)等4個不同的選項。點擊stepl,便打開了FIR濾波器核的參數設置窗口,如圖3所示。

由圖3可見,濾波器的系數精度為32位,器件為CycloneⅢ,結構為并行濾波器,結構選擇了1級流水線,濾波器由LC邏輯宏單元構成,系數數據存于FPGA的M9K模塊中,1個輸入通道,32位有符號并行輸入,全精度數據輸出。設定后會直接顯示濾波器的頻率響應(frequency res-ponse)或時域響應及系數值(timeresponse & coefficeient values)。由其頻率響應圖可以看出,此FIR濾波器為低通濾波器。如果不符合設計要求,則可以通過對Edit Coefficient Set選項,對濾波器進行重新配置。

濾波器相關文章:濾波器原理

濾波器相關文章:濾波器原理

低通濾波器相關文章:低通濾波器原理

電源濾波器相關文章:電源濾波器原理

高通濾波器相關文章:高通濾波器原理 數字濾波器相關文章:數字濾波器原理

評論