基于Zynq的OLED驅(qū)動(dòng)設(shè)計(jì)

OLED具備自發(fā)光、不需背光源、對(duì)比度高、厚度薄、視角廣、反應(yīng)速度快、可用于撓曲性面板、使用溫度范圍廣、構(gòu)造及制程較簡(jiǎn)單等優(yōu)異特性,被認(rèn)為是下一代的平面顯示器新興應(yīng)用技術(shù)。目前OLED的驅(qū)動(dòng)大部分都是基于STM系列 ARM芯片和傳統(tǒng)FPGA芯片。為適應(yīng)Xilinx最新平臺(tái)Zynq的人機(jī)交互需要,提出一種基于Zynq的OLED驅(qū)動(dòng)設(shè)計(jì)方法。文章闡述了OLED的特性和SPI控制方式,給出了設(shè)計(jì)流程和硬件電路圖。利用Zynq的PL部分完成了OLED驅(qū)動(dòng)的IP核,利用Zynq的PS部分實(shí)現(xiàn)了OLED的驅(qū)動(dòng)程序設(shè)計(jì)。通過(guò)AXI總線實(shí)現(xiàn)PL和PS的通信。最后通過(guò)測(cè)試程序,實(shí)現(xiàn)了字母、數(shù)字和點(diǎn)陣圖像的實(shí)時(shí)顯示。解決了基于Zynq器件在廣電儀器和電力儀表儀器中人機(jī)交互的工程技術(shù),具有集成度高、可移植性強(qiáng)和通用性好等優(yōu)點(diǎn)。

本文引用地址:http://www.czjhyjcfj.com/article/263551.htm1 引言

隨著近幾年嵌入式技術(shù)的飛速發(fā)展和廣泛應(yīng)用,人機(jī)交互成為嵌入式設(shè)備的迫切需要。為適應(yīng)Xilinx最新平臺(tái)Zynq的人機(jī)交互需要,提出一種基于Zynq的OLED驅(qū)動(dòng)設(shè)計(jì)方法。

有機(jī)發(fā)光二極管(Organic Light-Emitting Diode,OLED)由于同時(shí)具備自發(fā)光、不需背光源、對(duì)比度高、厚度薄、視角廣、反應(yīng)速度快、可用于撓曲性面板、使用溫度范圍廣、構(gòu)造及制程較簡(jiǎn)單等優(yōu)異特性,被認(rèn)為是下一代的平面顯示器新興應(yīng)用技術(shù)。

Xilinx最新平臺(tái)Zynq將處理器的軟件可編程能力與FPGA的硬件可編程能力實(shí)現(xiàn)完美結(jié)合,以低功耗和低成本等系統(tǒng)優(yōu)勢(shì)實(shí)現(xiàn)良好的系統(tǒng)性能、靈活性和可擴(kuò)展性。

目前OLED的驅(qū)動(dòng)大部分都是基于STM系列ARM芯片和傳統(tǒng)FPGA芯片。在Zynq上,Xilinx提供了Linux演示實(shí)例,但無(wú)裸機(jī)源碼,無(wú)法滿足實(shí)時(shí)性比較強(qiáng)的工程實(shí)際需求。

文章詳細(xì)闡述了基于Zynq的OLED驅(qū)動(dòng)設(shè)計(jì)步驟和方法,并且在基于Zynq的開(kāi)發(fā)板ZedBoard上實(shí)現(xiàn)了實(shí)時(shí)顯示字母、數(shù)字和點(diǎn)陣圖像,為Zynq在儀器儀表領(lǐng)域?qū)崿F(xiàn)人機(jī)交互提供了技術(shù)支撐。

2 OLED驅(qū)動(dòng)設(shè)計(jì)流程

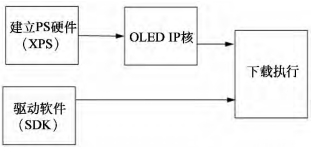

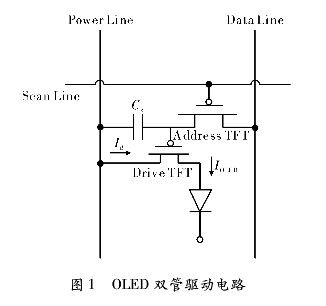

Zynq是一個(gè)ARMPS+PL結(jié)構(gòu),其中PL部分就是傳統(tǒng)意義的FPGA,可以方便地定制相關(guān)外設(shè)IP,也可以進(jìn)行相關(guān)的算法設(shè)計(jì),和使用普通FPGA完全一樣。如果不使用PL,Zynq的PS部分和普通的ARM開(kāi)發(fā)一樣。Zynq最大的特點(diǎn)是可以利用PL部分靈活地定制外設(shè),掛在PS上,而普通的ARM,外設(shè)是固定的。因此,Zynq的硬件外設(shè)是不固定的,這也是Zynq靈活性的一個(gè)表現(xiàn)。OLED在Zynq上是連接在PL上,因此需要把OLED對(duì)應(yīng)引腳掛在PS的硬件上,然后設(shè)計(jì)OLED IP核,再通過(guò)SDK設(shè)計(jì)驅(qū)動(dòng)程序,OLED驅(qū)動(dòng)設(shè)計(jì)流程如圖1所示。

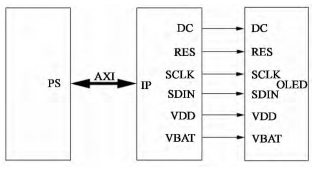

ZedBozrd控制OLED的主要方法是:自行設(shè)計(jì)一個(gè)IP核,對(duì)OLED的6個(gè)控制信號(hào)和電源信號(hào)進(jìn)行邏輯設(shè)計(jì)和引腳約束,通過(guò)AXI總線,把OLED的IP核和PS聯(lián)系起來(lái)。在PS部分編寫(xiě)相應(yīng)的驅(qū)動(dòng)程序,即可實(shí)現(xiàn)對(duì)OLED的控制,如圖2所示。

圖1 OLED驅(qū)動(dòng)設(shè)計(jì)流程

圖2 OLED系統(tǒng)設(shè)計(jì)圖

因此,要實(shí)現(xiàn)OLED顯示功 能,主要做以下幾個(gè)方面工作:設(shè)計(jì)Zynq硬件系統(tǒng)(PS部分)、設(shè)計(jì)自己的IP核和PS部分驅(qū)動(dòng)程序設(shè)計(jì)。

3 建立Zynq硬件系統(tǒng)和OLED IP核

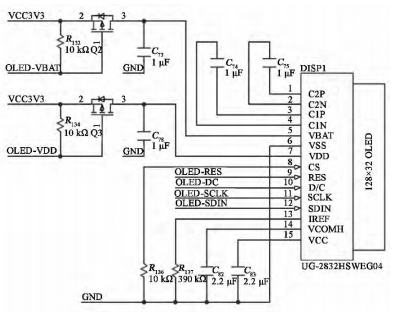

Zynq的開(kāi)發(fā)板ZedBoard上使用Inteltronic/Wisechip公司的OLED顯示模組UG-2832HSWEG04,分辨率為128×32,是一款單色被動(dòng)式顯示屏,驅(qū)動(dòng)電路采用所羅門科技的SSD1306芯片。具體電路如圖3所示。根據(jù)原理圖可知,ZedBoard開(kāi)發(fā)板使用的OLED采用SPI方式控制,SPI模式使用的信號(hào)線和電源線有如下幾條:

RST(RES):硬復(fù)位OLED;

DC:命令/數(shù)據(jù)標(biāo)志(0,讀寫(xiě)命令;1,讀寫(xiě)數(shù)據(jù));

SCLK:串行時(shí)鐘線;

SDIN:串行數(shù)據(jù)線;

VDD:邏輯電路電源;

VBAT:DC/DC轉(zhuǎn)換電路電源。

在SPI模式下,每個(gè)數(shù)據(jù)長(zhǎng)度均為8位,在SCLK的上升沿,數(shù)據(jù)從SDIN移入到SSD1306,并且是高位在前的。

圖3 OLED原理圖

Zynq的硬件系統(tǒng)是指在PL中配置相關(guān)外設(shè),掛載到PS中,作為PS部分的外設(shè)使用。OLED驅(qū)動(dòng)主要用到6個(gè)IO口,在生成硬件系統(tǒng)時(shí),只需要利用Xilinx的嵌入式工具XPS生成最小硬件系統(tǒng),然后把OLED的相關(guān)引腳添加到最小硬件系統(tǒng)中。主要過(guò)程如下:

(1)根據(jù)芯片型號(hào),根據(jù)XPS工具設(shè)計(jì)流程,生成Zynq的最小硬件系統(tǒng)。

(2)在最小硬件系統(tǒng)中,添加外設(shè)IPmy_oled,把OLED的SPI引腳添加到工程中。添加一個(gè)6位寄存器,每位和SPI引腳對(duì)應(yīng)。

(3)my_oledIP核邏輯設(shè)計(jì)主要完成IP核引腳添加、端口映射和用戶邏輯功能。首先要對(duì)設(shè)計(jì)的IP核添加引腳,在系統(tǒng)生成的MPD文件中,添加OLED的相關(guān)引腳端口和方向信息。

在MPD文件中,在PORT下添加OLED的相關(guān)引腳和方向信息,具體代碼如下:

PORTDC=“ ”,DIR=O

PORTRES=“ ”,DIR=O

PORTSCLK=“ ”,DIR=O

PORTSDIN=“ ”,DIR=O

PORTVBAT=“ ”,DIR=O

PORTVDD=“ ”,DIR=O

(4)在系統(tǒng)生成的my_oled.vhd文件中,用VHDL語(yǔ)言進(jìn)行端口設(shè)計(jì),主要進(jìn)行以下兩個(gè)設(shè)計(jì)。

聲明IP和用戶6個(gè)信號(hào)和電源的端口。代碼如下:

DC ∶outstd_logic;

RES ∶outstd_logic;

SCLK ∶outstd_logic;

SDIN ∶outstd_logic;

VBAT ∶outstd_logic;

VDD ∶outstd_logic;

將用戶端口和IP核端口進(jìn)行映射,代碼如下:

DC =>DC,

RES =>RES,

SCLK =>SCLK,

SDIN =>SDIN,

VBAT =>VBAT,

VDD =>VDD,

評(píng)論