一種基于HD-SDI技術的高清圖像處理系統設計

摘要:隨著圖像處理技術及傳感器技術的不斷發展,高清數字圖像取代模擬圖像成為一種趨勢。設計了一種基于HD-SDI技術的高清圖像處理系統,可通過FPGA+DSP架構對1080P全高清圖像進行采集和字符疊加,并實時進行目標提取和偏差量計算。疊加視頻可通過DVI數字接口或模擬接口實時顯示。利用圖像高分辨率特性,系統可實現運動目標精確跟蹤。

本文引用地址:http://www.czjhyjcfj.com/article/263277.htm引言

隨著數字視頻的迅速發展,高清數字圖像代替模擬圖像成為必然趨勢。光電系統采用全高清圖像技術,不僅能大大提高顯示效果,而且能顯著提高系統的跟蹤精度。因此,高清圖像處理系統的開發成為光電系統技術發展必須突破的關鍵技術之一。SDI(Serial Digital Inter face)即串行數字接口,其標準由移動圖像和電視工程師協會(SMPTE)制定,在當今的廣播和視頻產品領域得到了廣泛的應用。標準規定如何通過同軸電纜在設備間傳送未經壓縮的串行數字視頻數據。

在非編后期制作、廣播電臺等領域,基于HD-SDI(High Definition-Serial Digital Interface)高清電視應用較為廣泛,在1.485Gb/ s、1.001 Gb/s的信號速率條件下傳輸的接口規格都符合標準SMPTE-292M。該接口攝像機既能保證光電系統高清顯示的要求,又能滿足目標實時跟蹤的要求。

本文設計了一種基于HD-SDI的高清圖像處理系統,可滿足光電系統實現圖像高清顯示和目標跟蹤的要求,具有較好的平臺兼容性的要求。

1 系統組成

HD-SDI攝像機將高清視頻通過75 Ω同軸電纜實時傳送到高清圖像處理系統。系統對圖像進行處理后,將視頻信號送到數字顯示終端進行顯示。

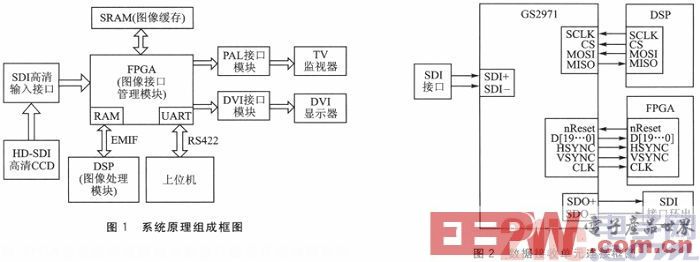

由于全高清數字圖像處理系統涉及大量數據的運算及邏輯控制,系統的控制體系采用FPGA+DSP的結構形式。FPGA進行圖像采集、存儲、輸出顯示和整個系統的邏輯控制;DSP作為數字信號處理核心,則主要用來運行圖像跟蹤算法及完成各種外設的初始化。系統的硬件組成包括數據接收單元—HD-SDI數字視頻輸入;數據發送單元—HD-SDI、DVI、AV視頻輸出;圖像存儲單元—4個72 Mb SRAM;通信單元—RS422接口。系統組成框圖如圖1所示。

DSP選用TI公司的TMS320C26414,FPGA采用ALTERA公司的EP3C120F780,二者通過32位數據總線進行視頻數據和其他參數傳輸。數據輸入接口采用HD-SDI高清視頻接口芯片對高清攝像機的視頻信號進行解碼,FPGA接收解碼視頻信號后進行圖像存儲和頻率轉換,并將圖像數據傳給DSP進行窗口檢測、自適應圖像分割、相關匹配等運算,獲取目標位置相對光軸中心的偏差量。同時,FPGA通過片內雙口RAM與DSP進行數據通信,完成如字符顯示與消隱等功能,以方便人機界面操作。上位機通過RS422接口與FPGA進行數據通信,將測角數據、控制參數、設備狀態等信息傳遞給圖像處理系統,圖像處理系統則將測偏量信息傳遞給上位機進行目標跟蹤。

圖像處理是光電系統的重要組成部分,在設計中需保持圖像處理系統的通用性和開放性。采用了模塊化設計思想,并采用通用通信接口代替總線與上位機通信,可保證硬件適用于不同的系統平臺。各模塊分別完成以下功能:

①FPGA完成圖像采集、圖像顯示接口控制、外部存儲器的讀寫邏輯控制及與上位機的通信。

②DSP與FPGA之間通過雙口RAM實現通信,并通過FPGA讀寫SRAM實現目標提取和字符疊加功能。DSP實現包括目標檢測、模板匹配、電子穩像等多種圖像算法。

③SRAM是外擴的圖像存儲器,FPGA通過ping-pong方式將采集到的高清數字圖像存儲在SRAM中并輸出給DSP和顯示接口。

④數據接收單元由高速SDI接口實現高清攝像機輸入視頻解碼。

⑤數據發送單元實現DVI、AV與SDI輸出視頻的編碼功能。

2 數據接收單元

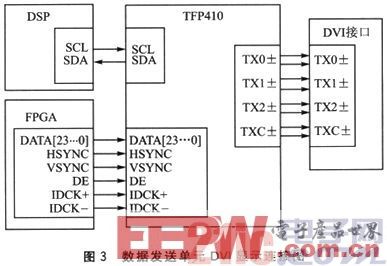

數據接收單元由SDI解碼器組成。系統選用Gennum公司生產的GS2971對HD-SDI攝像機傳輸的視頻信號進行解碼,之后將高清視頻信號的像素時鐘、行、場及視頻數據傳給FPGA。數據接收單元連接框圖如圖2所示。

GS2971是一款自帶線纜均衡功能的單端口輸入解碼芯片。支持3Gb/s、HD、SD SDI串行數據傳輸速度,最高支持4:2:2 10位色深表現,分辨率可達1080P。內置HD-SDI解串器簡化了外部FPGA的邏輯解串功能。GS2971的初始化采用I/O電平控制與SPI接口相結合的方法,可被配置為20位數據輸出和10位數據輸出。當配置為20位數據輸出時,亮度信息和色度信息分別占10位數據線,時鐘為74.25 MHz;配置為10位數據輸出時,亮度和色度信息合成輸出,時鐘為148.5 MHz。本系統中,將GS2971配置為20位數據輸出模式,GS2971支持一路SDI信號環路輸出,可供系統實時檢測SDI信號輸入是否正常。

3 數據發送單元

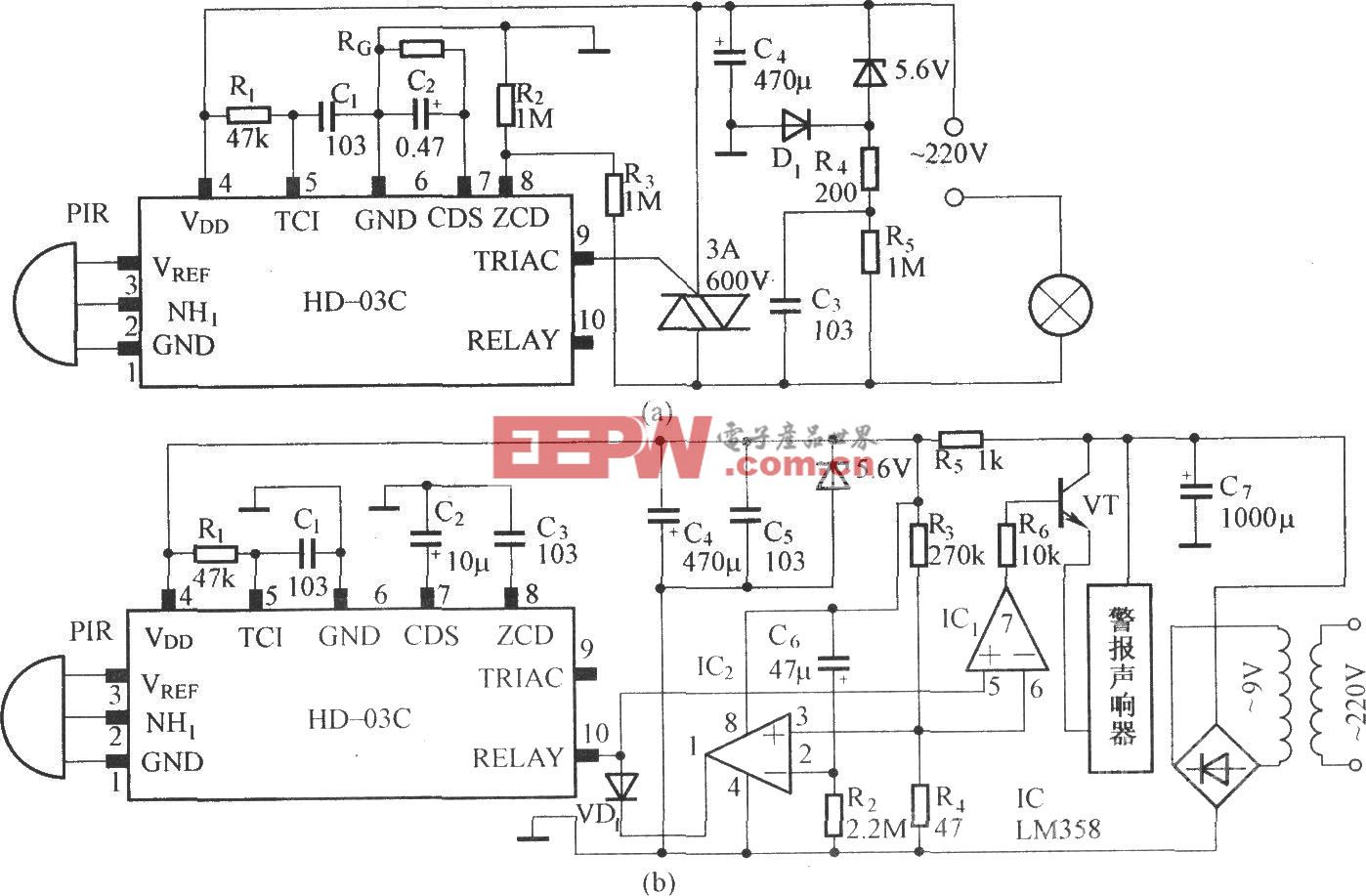

系統設計的數據發送單元由一個DVI編碼器和一個PAL編碼器組成。其中,DVI編碼器將數字信號轉換為差分信號,傳遞給DVI接口高清顯示器。DVI接口需實現1080P高清顯示,是系統數據發送單元的關鍵環節。

針對圖像輸出接口的不同要求,選擇NXP公司的SAF7129實現圖像的PAL制式輸出;選擇TI公司的TFP410實現DVI圖像輸出。其中,DVI顯示為數字信號輸出,與傳統的VGA模擬信號相比,采用DVI數字信號不會引起像素抖動和相鄰像素間的干擾,顯示器不會造成幾何失真,大大提高了畫面質量,顯示畫面細膩、清晰,因此設計時將DVI接口作為系統的主顯示通道。PAL制式為模擬信號輸出,可以兼容光電系統在特殊情況下的顯示需求。數據發送單元DVI顯示連接如圖3所示。

TFP410支持從VGA到UXGA(25~165 MHz)格式的像素速率,具有12位雙邊和24位單邊兩種輸入模式,可以通過I2C總線進行芯片工作模式配置。TFP410主要通過DE引腳的高低電子來決定發送信號類型。當DE為高電平時,發送像素編碼數據;當DE為低電平時,發送同步信號以及控制信號。

本設計通過I2C總線來配置編碼器,編碼器采用24位單邊輸入模式,單邊輸入時鐘,下降沿觸發。采用I2C總線可以快捷地在線調整參數配置,對編碼器高速輸入信號的時鐘沿進行調整,有效減少圖像噪聲和串擾。

fpga相關文章:fpga是什么

cdma相關文章:cdma原理

評論