基于FPGA的高速訪問USB設備設計

摘要:針對FPGA訪問USB設備存在傳輸速率低、資源消耗大、開發復雜的缺點,提出了一種將ARM處理器與FPGA相結合實現高速訪問USB設備的方案。該方案利用ARM處理器的USB Host讀取USB設備數據井緩存于高速內存,采用乒乓機制通過SRAM接口將數據傳給FPGA。經測試,數據傳輸速率可以達到48 Mbps。該方案具有開發難度小,資源占用率低和傳輸速率高的特點,適合于FPGA高速讀取大量外部數據。

本文引用地址:http://www.czjhyjcfj.com/article/263272.htm引言

目前FPGA通過USB接口獲取USB設備中數據的方案大致分為兩大類,一類為在FPGA內部實現USB設備控制,另一類為在FPGA外部實現USB設備控制。在FPGA內部實現的方案需要在FPGA內部實現USB控制器,在內部實現或者外接USB收發器。該方案的實現具有較大難度,同時由于USB協議和文件系統都相當復雜,需要使用相當多的FPGA資源,因此完全不能滿足快速開發和低FPGA資源占用率的要求。在FPGA外部實現的方案通常使用單芯片的USB解決方案,典型的方案有兩種:一種是集成了USB控制器和USB收發器,但需自行實現文件系統,如美國Cypress公司的CY7C67300;另一種是實現了包括文件系統在內的所有USB讀取U盤所需的軟硬件,只需要FPGA發送命令進行控制即可實現讀取U盤,如南京沁恒電子的CH376。在這兩類方案中,CY7C67300集成度高,但其只支持USB 1.1,傳輸速率較低;同時需要FPGA對其進行配置和控制及實現文件系統,FPGA端的開發量較大。CH376支持USB2.0接口,是一個真正的單芯片解決方案;但CH376只支持FAT16/32文件系統,不支持NTFS文件系統,無法讀取大于4 GB的大文件。另外,CH376需要FPGA進行配置和控制,因此需要實現CH376的控制邏輯并占用一定的FPGA資源。

由于現有方案均存在數據傳輸速率低、FPGA開發量大的缺點,本文提出了一種使用ARM+FPGA的方案,通過ARM處理器讀取USB設備數據并傳輸給FPGA,從而實現FPGA從USB設備獲取數據。該方案既能達到較高的數據傳輸速率,又能降低FPGA開發量,同時還具有很高的靈活性。

1 系統設計

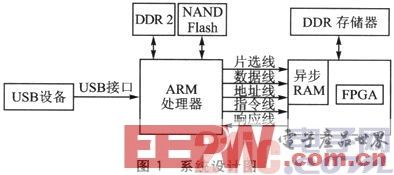

本方案的系統設計如圖1所示。該系統由ARM處理器、FPGA和USB設備構成,FPGA通過內部開辟的異步RAM空間接收數據,ARM處理器負責將USB設備中數據通過并行總線轉發給FPGA,USB設備支持常見的U盤、照相機、移動硬盤等支持USB接口的從設備。本設計還將ARM處理器的兩個引腳與FPGA的通信。指令線用于ARM向FPGA發送準備進行數據傳輸的指令;響應線用于FPGA在接收到ARM的通知并準備好后響應ARM。與FPGA相連的DDR存儲器用于高速緩存大量圖像數據,支持常見的DDR、DDR2和DDR3等類型。

1.1 ARM處理器選擇

本方案選用的ARM處理器為韓國三星公司的S5PV210。S5PV210是一款基于ARM Cortex—A8內核的RSIC處理器,該芯片擁有強大的計算能力、豐富的內部資源和外部接口,主頻高達1 GHz,同時它還擁有優化的外部存儲器接口。外部存儲器接口為異步接口,時鐘頻率為133MHz,位寬為16位,具有完善且可調的時序控制功能,可用于連接ROM、SRAM、oneNAND、NAND Flash等多種存儲器,能滿足在高端通信服務中的數據帶寬要求。本方案使用這個接口完成數據從ARM處理器到FPGA的高速傳輸。

1.2 ARM與FPGA接口設計

本方案將FPGA異步RAM連接在ARM處理器的XM0內存總線上,作為一個位寬為16位的SRAM使用,其對應的硬件地址為0x10000000到0x1000 1002,共4 098字節。由于異步RAM的位寬為16位,故只需使用地址線ADDR 1~ADDR 13。指令線連接ARM處理器的GPIO引腳,方向為輸出,高電平有效。響應線連接ARM處理器的中斷引腳,方向為輸入,上升沿有效。

1.3 軟件設計

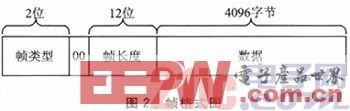

在本方案中,ARM處理器以幀為單位向FPGA傳輸數據。每幀長度為4 098字節,其中,幀頭長度為2字節,數據長度為4 096字節。幀格式如圖2所示。

幀類型的取值為:此幀不是最后幀為00,此幀是最后幀則為11。幀長度為幀數據的長度,以字節為單位。

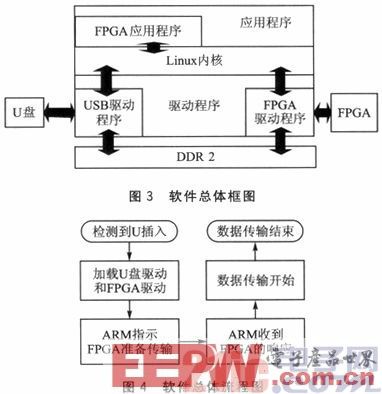

本方案所設計的軟件分為兩個部分一一驅動程序和應用程序,軟件總體框圖如圖3所示。驅動程序在Linux系統中注冊硬件并提供控制硬件的功能函數,以供應用程序調用。應用程序使用驅動程序提供的功能函數控制硬件,完成整個傳輸過程。軟件總體流程圖如圖4所示。

1.3.1 驅動程序設計

本方案涉及3種驅動程序:USB驅動程序、文件系統驅動程序和FPGA驅動程序。

Linux系統有豐富完善的USB設備和文件系統支持。本方案使用Linux系統中自帶的USB Mass Storage驅動程序和文件系統驅動程序,自行編寫FPGA驅動程序。FPGA驅動程序基于Linux系統字符設備驅動程序模型進行編寫。FPGA驅動程序的主要函數有初始化函數init()、寫入中斷服務函數write_int()、寫入函數write()。

初始化函數init()首先將FPGA異步RAM對應的硬件地址0x10000000~0x10001002映射為Linux系統中的內存虛擬地址A到A+4098(設映射的內存虛擬地址起始為A),實現在Linux系統中直接向異步RAM寫入數據。然后,設置指令線、響應線所對應的寄存器。將指令線的方向設置為輸出,并輸出低電平;響應線的方向設置為中斷輸入。最后,函數將響應線中斷服務函數設置為write_int()。

寫入函數write()與寫入中斷服務函數write_int()配合,完成一次數據傳輸:

①當應用程序調用寫入函數后,函數首先設置指令線為高電平指示FPGA準備傳輸數據,然后將驅動程序置于休眠狀態,等待喚醒。

②FPGA收到指令后判斷現在能否傳輸數據,如果能,則在中斷線上發送一個上升沿。ARM處理器捕捉到該上升沿后,調用write_int(),喚醒驅動程序。

③驅動程序被喚醒后,繼續執行write()。write()函數首先根據應用程序提供的參數生成幀頭,并將幀頭寫入地址ADDR和ADDR+1,完成幀頭的傳輸。隨后將數據寫入地址ADDR+2及其后的地址,完成數據的傳輸。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

fpga相關文章:fpga是什么

linux相關文章:linux教程

評論