ARM存儲器之:存儲管理單元MMU

| 注意 | ARMv6體系結構不包含微頁,如果打算創建一個很容易移植到以后體系結構的系統,則建議在該系統中避免使用1KB微頁。 |

15.5.6域(domain)和存儲器訪問權限

域指的是一些段、大頁或者小頁的集合。編程的中,設計者最多可以使用16個域,每個域的訪問控制特征由CP15中的c3中的兩位控制。

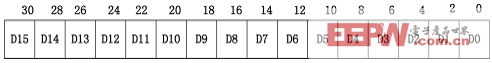

CP15中的寄存器c3的格式如圖15.34。

圖15.34CP15寄存器c3編碼格式

其中,每兩個位控制一個域的訪問控制特性,其編碼及對應的含義如表15.29所示。

表15.29 域訪問控制字段編碼及含義

控制位編碼 | 訪問類型 | 含義 |

0b00 | 無訪問權限 | 這時訪問該域將產生訪問失效 |

0b01 | 客戶類型(client) | 根據頁表中地址變換頁表項的域訪問權限控制位決定是否允許特定的存儲訪問 |

0b10 | 保留 | 使用該值會產生不可預知的結果 |

0b11 | 管理者權限(Manager) | 不考慮頁表中頁表項內的訪問控制權限位,所以這種情況下不產生訪問失效 |

綜上所述,有兩種不同的控制來管理一個任務的存儲器訪問權限。

·管理者(manager)用于主控(primarycontrol),不考慮每個段、大頁和小頁的訪問權限。

·客戶(client)使用頁表中的訪問權限用于次控(secondarycontrol)。

當多個段或者頁從屬于一個域時,這些段或者頁的訪問權限可以很容易的由域來統一控制。存儲器采用這種管理策略將不同的存儲單元“打包”。

| 注意 | 即使不使用MMU提供的虛擬存儲功能,仍然可以把這些內核用作簡單的存儲保護單元。首先將虛擬存儲空間直接映射到物理存儲空間,然后為每個任務分配一個不同的域,最后使用這些域來保護睡眠任務(通過將它們的域訪問設置成不可訪問)。 |

15.5.7與TLB相關的操作

(1)清除TLB

如果操作系統改變了頁表中的數據,那么緩存在TLB中的轉換數據可能就不再有效了。存儲器核有一些CP15命令用于清除TLB,從而使TLB中的數據作廢。表15.30是一些可用的命令:清除所有TLB數據,清除指令TLB,清除數據TLB,也可以一次只清除一行TLB數據。

表15.30 清除TLB的CP15命令

命令 | MCR指令 | Rd的值 | 支持的內核 |

使所有TLB無效 | MCRp15,0,Rd,c8,c7,0 | 0 | ARM720T、ARM920T、ARM922T、ARM926EJ-S、ARM1022E、ARM1026EJ-S、StrongARM、Xscale |

按行使TLB無效 | MCRp15,0,Rd,c8,c7,1 | 要使之無效的虛擬地址 | ARM720T |

使指令TLB無效 | MCRp15,0,Rd,c8,c5,0 | 要使之無效的虛擬地址 | ARM920T、ARM922T、ARM926EJ-S、ARM1022E、ARM1026EJ-S、StrongARM、Xscale |

按行使指令TLB無效 | MCRp15,0,Rd,c8,c5,1 | 要使之無效的虛擬地址 | ARM920T、ARM922T、ARM926EJ-S、ARM1022E、ARM1026EJ-S、StrongARM、Xscale |

使數據TLB無效 | MCRp15,0,Rd,c8,c6,0 | 要使之無效的虛擬地址 | ARM920T、ARM922T、ARM926EJ-S、ARM1022E、ARM1026EJ-S、StrongARM、Xscale |

按行使數據TLB無效 | MCRp15,0,Rd,c8,c6,1 | 要使之無效的虛擬地址 | ARM920T、ARM922T、ARM926EJ-S、ARM1022E、ARM1026EJ-S、StrongARM、Xscale |

存儲器相關文章:存儲器原理

評論