可編程語音壓縮專用處理器設計

摘 要:為了提高通信系統的保密性,降低制造成本,需要進行專用處理器的設計。基于正弦激勵線性預測(SELP)算法模型,設計了一款多速率語音專用處理器。芯片使用可重構體系結構和超長指令字(VLIw),優化了高復雜度函數。仿真結果表明:該處理器對O.6 kb/s速率SELP算法的執行效率明顯優于通用數字信號處理器(DSP)。處理器內部程序數據外部不可見,指令并行度顯著提高,常用函數可被修改,從而達到高保密性、低復雜度、易開發性。

關鍵詞:語音信號處理;語音壓縮;專用芯片;可重構體系結構;超長指令字

為了適應多種通信應用,需要使用不同的語音壓縮編碼算法。用數字信號處理器(DSP)實現存在編程難、保密性差、成本高等缺點。專用芯片(ASIC)只能實現單一算法,很難擴展,難以進行二次開發。

可重構體系結構,是指某一計算系統能夠利用可重用的硬件資源,根據不同的應用需求,靈活地改變自身結構,以便提供與之相匹配的功能。已有可重構體系實現了語音算法的某些特定部分,如自適應多速率算法中的代數碼本搜索、原型編碼器中的小波變換以及有限脈沖響應濾波器等,但使用協處理器使硬件規模仍然偏大,且只能對一類語音算法適用。

使用可重構體系結構設計了一種可編程專用語音編解碼芯片TRl00,指令系統使用超長指令字(VLIW),使語音編碼算法中常用的并行操作可以在該芯片上產生比通用DSP更高的執行效率。高復雜度子程序能夠被多種類型的語音算法使用,避免引入協處理器,降低了二次開發編程的工作量。片內存儲器在外部不能讀取,提高了系統的保密性。

1 SELP算法

算法采用自行開發的基于正弦激勵線性預測(SELP)模型的多幀聯合編碼算法,在線性預測正弦激勵模型的基礎上,引入多幀參數聯合矢量量化方法,進一步壓縮幀間冗余,使語音譜包絡信息得到較好表示,在O.6 kb/s的極低速率下,可懂度達到90%以上。

O.6 kb/s速率采用多幀聯合量化編碼技術,將相鄰3幀預測系數均轉為線譜對系數(LSP),采用基于模式的余量分裂多級矩陣量化(P-RS-MSMQ)算法。根據不同的信道狀況與質量要求,算法還包括0.8 kb/s、 1.2 kb/s和2.4 kb/s另3種速率壓縮方式,流程與O.6 kb/s算法基本相同,僅增加對余量信號的編碼過程,其中需要進行512點快速Fourier變換(FFT)運算。

2 TR100芯片體系結構設計

芯片工作主頻為20 MHz,采用取指譯碼執行3級流水線設汁,內部結構如圖1所示。

TRl00芯片采用粗粒度可重構體系結構,基本的可重構硬件單元包括存儲系統、運算單元、程序調度控制、寄存器、數據通路等。

存儲系統包括閃存存儲器(FLASH)和隨機存儲器(RAM)兩部分。芯片內部包含2個32 kB數據FLASH、5個4 kB數據RAM。6個地址寄存器與3個地址運算單元可以分別獨立存儲器的地址控制與選擇。

運算單元包括2個32 b增強型算術邏輯單元,可完成以加減運算為中心、包括規格化、算術移位、四舍五入等輔助邏輯的復雜運算功能;1個32 b乘法器;1個40 b乘累加器;1個16 b除法器。

程序調度控制有2級硬循環、比較跳轉、比較設置、調用/返回等單元。兩個可被同時訪問的寄存器組各包含19個32 b寄存器,支持分層窗口式訪問;6個32 b選通器作為數據通路將存儲系統與運算部件進行互聯。

3 超長指令字格式設計

在針對語音編碼算法的專用處理器設計中,VLIW指令設計方法是非常適用的,它能在低復雜度的控制邏輯水平上產生較高指令并行性,使芯片在低主頻下即可實現語音壓縮算法。由于對資源并行度要求較高的程序模塊數量不大,因此可以通過遍歷所有運算量較大的模塊,提取可用的指令并行模式,在硬件控制邏輯復雜度增加很小的前提下實現超長指令譯碼。

設計的VLIW指令系統包括基本指令形態和專用指令形態。基本指令形態包括1 6b、32b、48b、64 b等4種指令長度,并行程度低,用于設計對資源并行性要求不高的子程序。專用指令形態包括128 b、192 b、256 b等3種指令長度,并行程度高,用于設計算法中復雜度較高、要求資源高并行度的子程序。兩類指令形態格式相同,從而可以使用相同的譯碼器進行譯碼,簡化了電路設計。基本指令模塊和專用指令模塊分別從程序FLASH與程序RAM中取指,均能做到單周期取指單周期譯碼一單周期執行。指令格式包括4個字段:Length確定指令長度;SF確定本長度下選用的指令子格式;CF進行算子選擇;OP進行算子編碼。

4 算法程序向芯片的移植

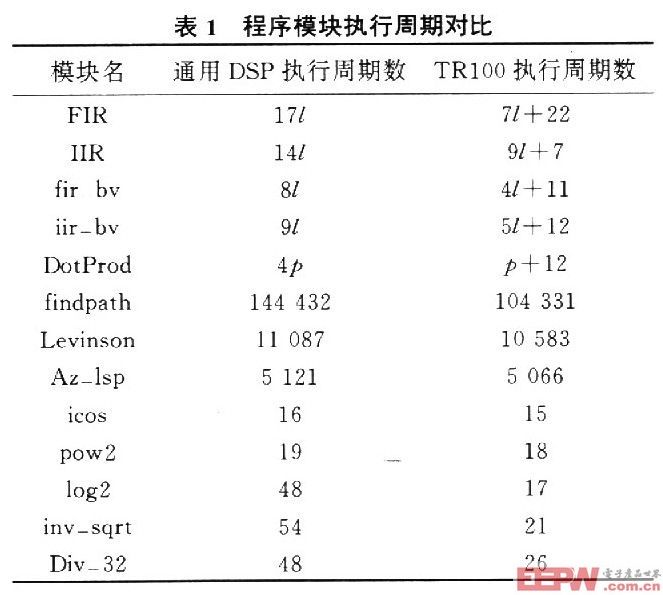

使用軟硬件協同設計,利用現有硬件的支持,可以編出高效率的代碼。表1是在TRl00上實現常用程序模塊的執行周期數與通用DSP對比結果,其中l表示濾波長度,p表示內積點數。

可以看到,壓縮算法中運算量較大的模塊,如濾波器、點積、矢量量化等,TR100的運行效率均明顯高于DSP,甚至達到兩倍以上。這是由于對于運算、存儲單元訪問密集的模塊,硬件體系結構中各個獨立單元可以用相應的指令格式并行訪問。而對線性預測系數(LPC)計算與轉換、數學函數等運算量不大、但各種語音算法都要使用的模塊,芯片的運行效率也與DSP基本相當。這就保證了在移植其他算法時,受程序執行效率的限制較小,而可以專注于算法功能的開發。注入功能可對基本指令與專用指令進行修改,便于開發者對現有程序進行擴充。

以加權矢量量化為例,說明芯片的運算效率。線譜對系數使用多幀聯合矢量量化,搜索運算量非常巨大。在SELP算法中,0.6 kb/s速率使用30維多級LSP碼本,容量為7.68 kB,搜索時需要計算每一碼本矢量bi與當前系數矢量x的加權距離di,權重為對角矩陣W,之后再找到最小的加權距離所對應的碼本矢量標號進行編碼。

使用一條256bit專用指令即可實現循環體內部操作:

與通用DSP的實現相比,本芯片可以在循環體內減少5次運算,本芯片對矢量搜索模塊的優化可減少近4MI/s的運算量。其中I為指令數。

5 芯片性能

數據FLASH寬度為16 b,存儲4個速率的不同碼本,碼本容量為199g kB,最大臨時數據變量使用19.8 kB,與C54xDSP所需的存儲空間相當。全部程序共5.7 k I,其中專用指令程序為2 kI。

0.6 kb/s速率算法各子模塊的運算量如表2。

在TRl00芯片上完成編解碼的運算復雜度為12.5 MI/s,明顯低于C54xDSP所需的40 MI/s。

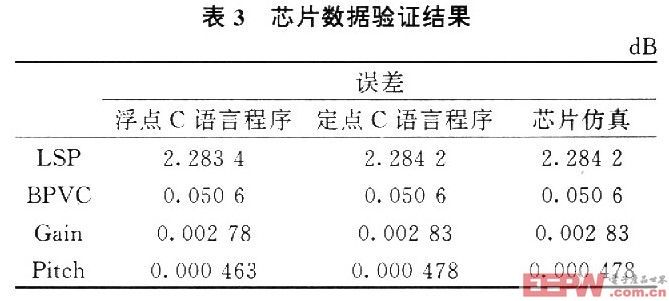

表3對比了浮點C語言程序、定點C語言程序以及芯片仿真3種情況下各個參數的重建誤差,使用91280幀中國軍標語音測試數據。

可以看出,海量數據測試出的定點C程序的各個重建參數誤差與芯片仿真的結果完全相同,由此可以說明芯片獲得的編碼碼流與重建語音與C程序的結果相同。

6 結 論

使用VLIW設計的可重構處理器能夠在相同硬件結構下實現不同的語音壓縮算法,由于針對算法中常用的運算密集模塊在體系結構和指令形態上進行了優化,該處理器對語音算法中計算、存儲密集度高的函數具備更高的指令并行性,從而獲得了更高的運行效率與更低的主頻,使功耗降低。算法程序外部完全不可見,提高了保密性。常用函數可以通過注入方式進行修改,避免了引入協處理器導致的難以擴充的缺點,并有效減小了芯片規模。

評論