采用高性能SRAM提高DSP密集型應用的性能

軍事與國防應用極大地受益于數字信號處理器(DSP),其廣泛應用于雷達、軟件無線電(SDR)、靈巧彈藥與目標探測系統、電子戰應用、飛機成像以及眾多其它應用。DSP借助其完美架構提供的精確處理能力可以顯著提高性能。關鍵DSP功能包括實時信號處理、超高吞吐量與可重編程功能。本文介紹了如何采用高性能四倍數據速率(QDR)SRAM而使整體DSP系統性能至少提高兩倍(與使用SDRAM的傳統方法相比)的方法。

本文引用地址:http://www.czjhyjcfj.com/article/247534.htm數字信號處理

數字信號處理包含把信號轉換成數字形式后對其進行處理的方法,如:雷達處理。雷達系統基本上是產生可以通過定向天線饋送的脈沖。這些信號以光速傳播,而其路徑中的任何物體都會把一小部分的投射能量反射回雷達接收天線。計算發送和接收信號的差別可以了解物體的距離與速度。

DSP是雷達系統的基礎,可用于多種功能,如:脈沖壓縮、信號濾波和脈沖調制。沒有DSP,雷達系統就無法準確探測遠距離的物體。DSP與通用的微處理器不同,因為它們適用于設計FFT和FIR等濾波器時最常用的快速數學計算(乘法與加法)類型。一般情況下FFT濾波器可用于域轉換 – 從時域到頻域或者相反,而FIR濾波器用于信號分離與恢復。這幾種濾波器普遍存在于雷達設計中。

實現DSP有兩種主要的硬件方法:可編程DSP處理器與現場可編程門陣列(FPGA)。在這兩種方法中,DSP架構都非常適合DSP算法。

DSP處理器

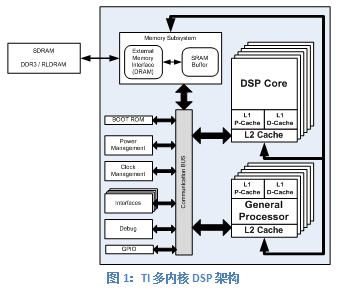

如圖1所示的TI多內核DSP等DSP處理器采用專用硬件計算每個周期的乘法運算。現代DSP處理器的指令集允許編程人員在單個指令中指定多個并行運算,一般在主算術運算進行的同時一次或多次從存儲器提取數據。另外,為了顯著改善每個時鐘周期的DSP性能,DSP架構目前包含并行運行的附加乘法器與加法器,從而可以在單個指令中編碼并行運算。

評論