基于FPGA平臺的工業電機最大效率實現

RIO架構目前已被用于多款系統中,如EUROelectronics等公司的系統。借助該架構,從產品原型設計到最終機械設備完成,EUROelectronics只用了3個月的時間。

縮短機械設計時間

無刷DC和永磁同步AC電機(PMSM)二者通常組成無刷DC電機(BLDC),其集成式控制非常復雜,是一個挑戰。許多機械制造商都缺乏構建嵌入式控制器方面的軟硬件設計經驗,難以讓嵌入式控制器在各種類型的模擬和數字傳感器上實時執行閉環控制。

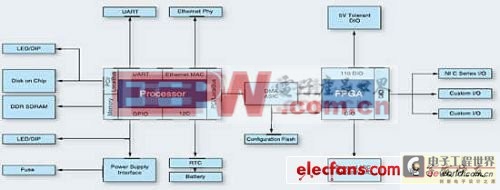

為了縮短嵌入式機械制造商的最終設計時間,本文介紹的方案在CompactRIO產品中集成了某種形式的RIO架構。這種基于FPGA的配置包括基于Virtex-5 LX85到Spartan-3的系統,以及基于Virtex-II 1M門的背板,配合基于PowerPC 603e的處理器,能夠滿足多種頻率和性能需求,如圖1所示。

圖1 在CompactRIO產品中集成了某種形式的RIO架構

在RIO框架中集成配置軟件實用程序和動態I/O重構功能可節約設置時間,而且終端應用編程人員和數字設計工程師還能重復使用有關資源。配置軟件能自動檢測系統中安裝的定制硬件。I/O外設的集成式診斷測試可確保I/O器件正常工作。

如果不安裝I/O電路,驅動程序軟件及相關API不能適當執行或返回具體器件的故障,就會出現問題。為解決上述問題,軟件開發人員通常會創建模擬子例程,臨時替代應用中的I/O電路代碼。這種方法難以立即開始應用開發,而且幾乎不能調試代碼。RIO中間件驅動程序架構包括相關功能,可將模擬代碼直接集成到函數驅動程序中,從而簡化代碼的重復使用與故障調試。

圖2 嵌入式中間件軟件設計分級圖

圖2所示為嵌入式中間件軟件設計分級圖。這種中間件驅動程序和系統服務在成千上萬種已經部署的機械設計應用中都證實了自己的功能。并行和多線程安全型嵌入式中間件驅動程序是RIO的有機組成部分。機械制造商可同時從多個線程調用多線程安全型和可再入函數,同時還能確保正常工作,避免阻塞現象,這對并行代碼的編寫和性能優化都是非常重要的特性。不具備可再入執行功能的驅動程序會影響性能,更糟的是還會導致崩潰。代碼必須等其他線程使用完每個函數后才能訪問函數。可再入性可避免代碼中任何不必要的依賴性。

BLDC和PMSM的定子纏繞方式有別。BLDC的定子旋轉時其纏繞方式可生成梯形反電勢電壓,而PMSM的電壓則為正弦曲線。

BLDC的成本高于AC電感電機,但在用高級算法控制情況下其節能性和性能更高。此外,BLDC還具有較高的可擴展性,能滿足極高功率和極高速應用的需求。

評論