基于Actel反熔絲FPGA的高速DDR接口設計

2 仿真及優化

在Actel 公司的編程環境IDE V9. 0 中進行編程仿真。使用Modelsim 6. 5d 進行行為仿真,仿真波形如圖8 所示。由圖8 可見變換后數據符合預期,功能實現正確。

使用Modelsim 6. 5d 進行布局布線后仿真,仿真波形如圖9 所示。由圖9 可見各路數據均存在毛刺,毛刺的最大寬度達到了1. 8ns,這超出了DAC 器件對于輸入并行數據相位差小于1ns 的要求。可能導致DAC 采樣錯誤。

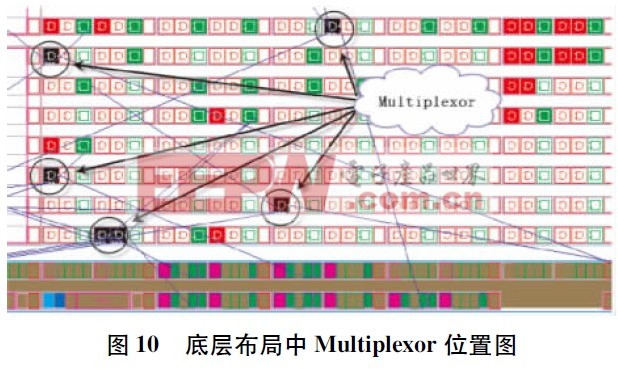

分析最終輸出數據毛刺產生的原因,應當是每路數據的14bit 單獨信號之間路徑的延時不同導致的。而數據在輸出之前大部分環節都是由全局時鐘進行同步處理,可以保證嚴格的同步,除了選擇器Multiplexor 輸出到IO 端口部分走線,因為在Multiplexor的輸出環節不會再有時鐘采樣,因此該部分多路信號延遲差異無法消除。檢查布局布線后底層的布局圖,如圖10 所示,深黑色的單元即為Multiplexor,顯然各個Multiplexor 與對應IO 口的距離差別較大,驗證了之前的分析。

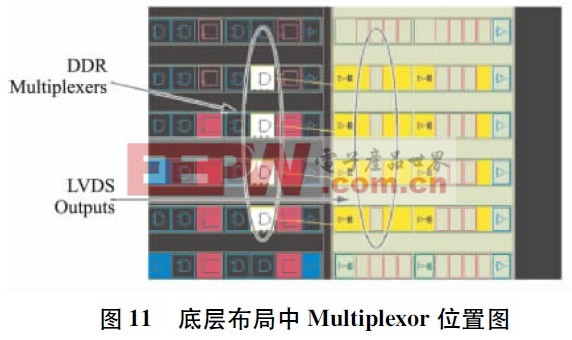

根據前段分析,對Multiplexor 的位置進行手動優化,即在底層布局圖中將所有Multiplexor 均調整到盡量接近IO 端口的位置,保證多路信號在Multiplexor后端延遲盡量一致,優化后鎖定這些Multiplexor的位置,如圖11 所示。

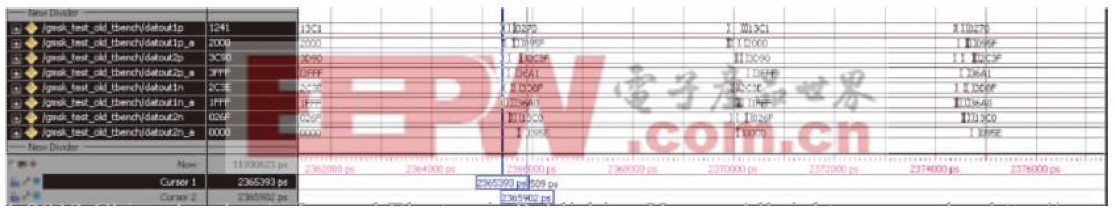

優化Multiplexor 布局后重新進行后仿真,仿真結果如圖12 所示。由圖12 可見,最大毛刺寬度僅為500ps 左右,完全滿足DAC 要求的1ns.可見,優化后的方案合理、可行的實現了要求的功能。

圖12 優化底層布局中Multiplexor 位置后的后仿真

文章中闡述的方法不僅僅局限于FPGA 與DAC之間的接口設計,也適用于FPGA 與其他高速芯片的通信,例如FPGA、DSP、SDRAM 等等支持DDR 接口的器件,同時,對于板級及單元級的通信,使用該方法可以有效降低線纜傳輸信號速率,使得系統各個環節的設計更為簡單。

3 結束語

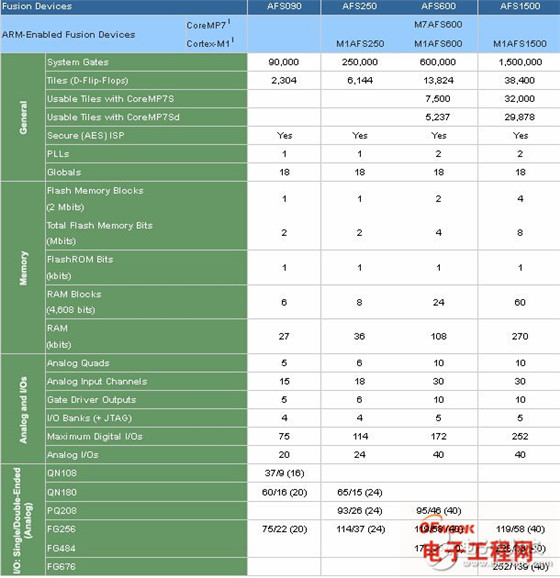

文章分析了Actel 公司反熔絲FPGA 相對于常用的SRAM 型FPGA 在衛星產品中應用的優點,并就一種常見的應用目標,提出基于Actel 公司RTAX-S 系列抗輻射反熔絲FPGA 的高速DDR 輸出接口的設計方法,并通過優化得到符合要求的結果,為反熔絲FPGA 在衛星產品中的高速設計、應用提供了技術保障。

評論