一種基于FPGA的多路數字信號復接系統設計

摘要 數字復分接技術是數字通信網中的一項重要技術,能將若干路低速信號合并為一路高速信號,以提高帶寬利用率和數據傳輸效率。文中在介紹數字復接系統的基礎上,采用VHDL對數字復分接系統進行建模設計和實現。并利用乒乓操作和先進先出存儲器(FIFO)對復接器進行設計,利用幀同步器對數據進行分接。以QuartusII8.0為仿真軟件,對設計進行仿真驗證,仿真結果表明,設計實現了復接系統,便于修改電路結構,增強了設計的靈活性,且節約了系統資源。

本文引用地址:http://www.czjhyjcfj.com/article/235202.htm數字通信系統中,為了提高信道的利用率,使多路信號在同一條信道上傳輸時互相不產生相干的方式稱為多路復用。在時分復用中,將時間劃分為若干時隙,各路信號在時間上占用各自的時隙,即多路信號在不同時間內被傳送,各路信號在時域中互不重疊。數字復接終端是將若干低速率碼流變換成一路高速率碼流的設備。應用可編程邏輯門陣列(FPGA)芯片實現復接系統便于修改電路結構,增強了設計的靈活性,并節約了系統資源。

1 多路復接系統設計要求

(1)實現兩路數據的同步復接。(2)支路速率為32 kbit·s-1。(3)按位復接。(4)幀同步碼字為10 bit:“1 0 1 1 0 1 0 01 1”。(5)幀長128 bit。

2 數字復接系統基本原理

2.1 數字復接系統

數字復接終端的作用是將低速數據碼流變換成高速數據碼流的設備。將兩個或兩個以上的支路數字信號按時分復用方式合并成單一的合路數字信號的過程稱為數字復接;完成數字復接功能的設備稱為數字復接器;在接收端將一路復合數字信號分離成各支路信號的過程稱為數字分接。數字復接器、數字分接器和傳輸傳道共同構成了數字復接系統。

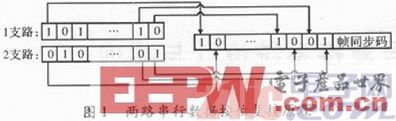

2.2 按位復接

復接的方式有:按位、按字和按幀復接等方式。本文采用按位復接的方法,方法是每次僅依次復接每一個支路的一位碼,又稱比特復接。復接后的碼序列中第一個時隙中的第一位表示第一路的第一位碼;第二位表示第二路的第一位碼;依此類推,則第n位表示第n路的第一位碼。2路串行數據按位復接原理框圖如圖1所示。

3 數字復接系統的建模與仿真

3.1 復接器總體設計方案

復接器的設計方案如下:首先對兩支路串行數據數字信號進行按位復接合成一路信號;用FIFO定義2個128 bit幀格式,幀同步碼為10 bit“1011010011”,采用乒乓操作對合路數據每118位依次存儲到FIFO中,即將合路數每118位插入一個幀同步碼,形成128位的幀。乒乓操作是輸入合路數據流通過輸入數據選擇單元等時地將數據流分配到兩個FIFO數據緩沖區。當FIFO緩沖區1寫入數據操作時,從FIFO緩沖區2中讀取數據操作;當FIFO緩沖區1讀數據操作時,FIFO緩沖區2中進行寫操作;如此循環,可實現2路數據復接,具體如圖2所示。

3.2 復接器關鍵模塊設計

(1)合路模塊。合路模塊功能是將兩路串行數據按位復接成一路數據,合路模塊輸出的是未接入幀同步碼的數據,對于各支路數據輸入需使用clksel時鐘作為控制。合路輸出為y信號,D0、D1是兩路串行數據,clksel是兩支路控制輸出信號。從仿真圖3中可看出,其能將D0和D1合成一路信號y輸出,仿真結果正確。

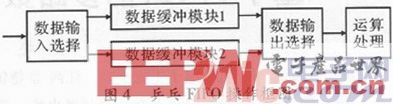

(2)乒乓操作FIFO模塊。乒乓操作FIFO模塊的功能是對合路數據加入幀同步碼。乒乓操作FIFO框圖如圖4所示。乒乓操作處理流程如下:輸入數據流通過輸入數據選擇單元將數據流分配到兩個數據緩沖區。在第1個緩沖周期中,將輸入的數據流緩存到數據緩沖模塊1;在第2個緩沖周期中,通過輸入數據選擇單元的切換,將輸入的數據流緩存到數據緩沖模塊2。同時,將數據緩沖模塊1緩存的第1個周期的數據通過輸出數據選擇單元的選擇,送到運算處理單元進行處理;在第3個緩沖周期,再次切換數據的進入與輸出緩沖模塊。

空滿信號的產生是設計FIFO的關鍵之一,本文通過異步的比較讀寫指針ptr以及讀寫指針的MSB進行判斷,然后產生兩個異步的空滿標志信號送入讀寫模塊進行同步,最后向外界輸出兩個同步的空滿信號。圖5的方框內可看出空判斷信號atmpty和滿判斷信號afull是取反的關系。當一個RAM數據讀完時,另一個RAM寫滿。

圖6中input,是M序列偽隨機碼,“10011101”作為測試信號。可認為M序列偽隨機碼是由兩支路信號合路而得到的信號。從仿真波形可看出,空滿判斷信號rmsb和wrsb1互為取反關系,滿足要求。rptr是讀地址信號從FIFO的首地址開始讀取數據的。wptr寫地址信號是從FIFO的第10個存儲單元開始寫入數據的,這是因為FIFO的前10個存儲單元使用的是做幀同步碼“1011010011”。zongshu信號端是隨機碼加入幀同步碼后的輸出。

3.3 分接器關鍵模塊設計

圖7是分接器的原理框圖。定時發生器為幀同步系統提供幀定位標志信號;幀同步系統用來檢測所傳輸數據碼流中的幀同步碼;比特分接電路則用于將串行數據轉換為并行數據。

fpga相關文章:fpga是什么

數字通信相關文章:數字通信原理

評論