淺析嵌入式系統設計中的低功耗技術

0 引言

本文引用地址:http://www.czjhyjcfj.com/article/227891.htm隨著科學的發展和微電子技術的不斷創新,嵌入式系統的應用越來越多,并已廣泛滲透到各個領域。嵌入式系統是以應用為中心,以電子技術和計算機技術為基礎,軟硬件可剪裁,能適應應用系統對功能、可靠性、穩定性、成本、體積、功耗等多方面嚴格要求的專用計算機系統。

在嵌入式系統的設計中,低功耗設計技術成為許多設計人員逐漸關注的問題,其原因在于嵌入式系統已被越來越多的應用在便攜式和移動性較強的產品中,而這些產品往往要靠電池來供電。實際上,這些年來,有關電池的儲能密度并沒有得到大的進步。而對于便攜設備,尤其是手持消費品而言,如果單靠提高電池容量來提高續航能力,似乎并不完全切合實際。因此,為提高設備性能,設計人員更需要從每一個細節考慮降低硬件系統本身的能耗。從而盡可能地延長電池的使用時間。事實上,低功耗設計也已經成為一個越來越迫切的問題,因而應該從硬件和軟件兩個方面來考慮嵌入式系統中的低功耗設計。

1 硬件的低功耗設計

1.1 硬件電路器件

由于現在絕大部分電路均采用集成電路CMOS工藝技術,這與以前的TTL工藝相比,本身就已經起到了降低電子元器件和整體系統功耗的作用,因此,應該繼續多采用CMOS集成電路工藝技術。另外,由于采用CMOS集成工藝技術,其電路靜態功耗很小(可忽略不計),而動態功耗較大,因為動態功耗是指電路高低電平翻轉時產生的功耗,在電路高低電平翻轉跳變沿期間,電流很大,存在較大功耗,所以,降低硬件電路功耗主要是降低電路動態功耗。動態功耗公式為:

![]()

其中,P代表CMOS芯片的動態功耗,C代表CMOS芯片的負載電容,V和f分別代表CMOS芯片的工作電壓和工作頻率。由公式可知,COMS硬件集成電路的功耗與工作電壓和工作頻率之間有密切的關系。因此,使用CMOS系列電路時,其不用的輸入端不要懸空,因為懸空的輸入端可能存在感應信號,并可能造成高低電平的轉換。同時,由于轉換器件的功耗很大,故應盡量采用輸出為高的原則。

1.2 低功耗外圍器件的選用

完成同樣的功能,電路的實現形式有多種。例如,盡可能地將嵌入式系統的內部存儲器RAM轉換為外部的閃存FLASH,因為在同樣條件下,讀內部RAM比讀外部FLASH會帶來更大的功耗。也可以利用分立元件、小規模集成電路,大規模集成電路甚至單片實現。通常使用的元器件數量越少,系統的功耗越低。因此,應盡量使用集成度高的器件,以減少電路中使用元件的個數,減少整機的功耗。 1.3 微處理器的選擇

嵌入式微處理器的功率消耗在嵌入式系統中占有相當大的部分,所以,選擇合適的處理器,對于嵌入式系統的整體功耗具有很大影響。微處理器的功耗主要分為兩部分: 內核功耗Pcore和外部接口控制器功耗Pio,總功耗等于兩者之和,即P=Pcore+Pio。對于Pcore,其關鍵在于供電電壓和時鐘頻率的高低; 而對于Pio,除了各個專門I/O控制器的功耗外,還有地址/數據總線寬度,因為總線寬度越寬,處理能力越大,功耗也越大。所以降低功耗,必需讓總線位數變窄。

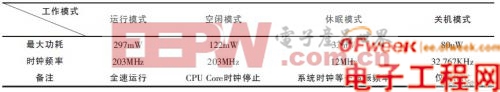

要降低微處理器內核的Pcore功耗,就必須想法降低處理器的工作電壓和時鐘頻率,其中降低微處理器的工作電壓是很有效的途徑,也是未來發展的趨勢,目前許多的嵌入式微處理器的工作電壓可降至2 V以下。并且高效率的處理器都提供有多種時鐘頻率和工作電壓的選擇,以便于最大限度地節約功耗。此外,在進行系統設計時,在工作電壓相差不大和系統處理能力許可的情況下,還應盡可能降低微處理器的時鐘頻率,現以起到節能的作用。以SAMSUNG S3C2410 (32 位ARM 920T內核) 為例,它就提供了四種工作模式: 正常模式、空閑模式、休眠模式、關機模式。各種模式下的功耗如表1所列。

不同工作模式的時鐘頻率與功耗對比表

由表1可知,CPU在全速運行的時候,比在空閑或者休眠時消耗的功率大得多。省電的原則就是讓正常運行模式遠比空閑、休眠模式少占用時間。在類似PDA的設備中,系統在全速運行時遠比空閑的時候少,所以,可以通過設置,使CPU盡可能工作在空閑狀態,使用時再通過相應的中斷喚醒CPU,以恢復到正常工作模式來處理響應的事件,然后再進入空閑模式。因此,設計系統時,如果處理能力許可,可盡量降低處理器的時鐘頻率。

也可以動態改變處理器的時鐘頻率以降低功耗,比如可關閉不需要的外設控制器,并在CPU空閑時降低時鐘頻率; 而在處于工作狀態時,再提高時鐘頻率以加快運行速度。

1.4 多CPU系統

盡管現在已有各種

評論