電子菜鳥入門電路基礎(chǔ)概念:TTL與CMOS電平 / OC門

集電極開路門(集電極開路 OC 或漏極開路 OD)

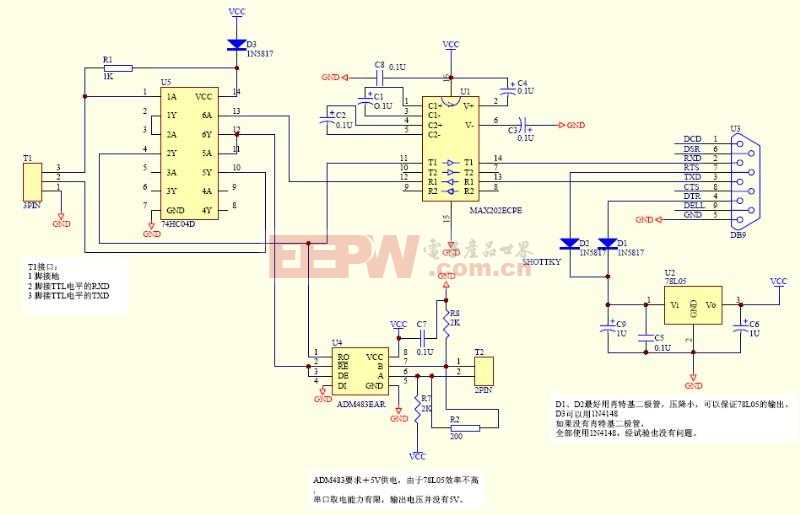

Open-Drain是漏極開路輸出的意思,相當于集電極開路(Open-Collector)輸出,即TTL中的集電極開路(OC)輸出。一般用于線或、線與,也有的用于電流驅(qū)動。

Open-Drain是對MOS管而言,Open-Collector是對雙極型管而言,在用法上沒啥區(qū)別。

開漏形式的電路有以下幾個特點:

a. 利用外部電路的驅(qū)動能力,減少IC內(nèi)部的驅(qū)動。 或驅(qū)動比芯片電源電壓高的負載.

b.可以將多個開漏輸出的Pin,連接到一條線上。通過一只上拉電阻,在不增加任何器件的情況下,形成“與邏輯”關(guān)系。這也是I2C,SMBus等總線判斷總線占用狀態(tài)的原理。如果作為圖騰輸出必須接上拉電阻。接容性負載時,下降延是芯片內(nèi)的晶體管,是有源驅(qū)動,速度較快;上升延是無源的外接電阻,速度慢。如果要求速度高電阻選擇要小,功耗會大。所以負載電阻的選擇要兼顧功耗和速度。

c. 可以利用改變上拉電源的電壓,改變傳輸電平。例如加上上拉電阻就可以提供TTL/CMOS電平輸出等。

d. 開漏Pin不連接外部的上拉電阻,則只能輸出低電平。一般來說,開漏是用來連接不同電平的器件,匹配電平用的。

正常的CMOS輸出級是上、下兩個管子,把上面的管子去掉就是OPEN-DRAIN了。這種輸出的主要目的有兩個:電平轉(zhuǎn)換和線與。

由于漏級開路,所以后級電路必須接一上拉電阻,上拉電阻的電源電壓就可以決定輸出電平。這樣你就可以進行任意電平的轉(zhuǎn)換了。

線與功能主要用于有多個電路對同一信號進行拉低操作的場合,如果本電路不想拉低,就輸出高電平,因為OPEN-DRAIN上面的管子被拿掉,高電平是靠外接的上拉電阻實現(xiàn)的。(而正常的CMOS輸出級,如果出現(xiàn)一個輸出為高另外一個為低時,等于電源短路。)

OPEN-DRAIN提供了靈活的輸出方式,但是也有其弱點,就是帶來上升沿的延時。因為上升沿是通過外接上拉無源電阻對負載充電,所以當電阻選擇小時延時就小,但功耗大;反之延時大功耗小。所以如果對延時有要求,則建議用下降沿輸出。

晶體管相關(guān)文章:晶體管工作原理

晶體管相關(guān)文章:晶體管原理 上拉電阻相關(guān)文章:上拉電阻原理

評論