電子菜鳥入門電路基礎概念:TTL與CMOS電平 / OC門

2.輸入低電平(Vil):保證邏輯門的輸入為低電平時所允許的最大輸入低電平,當輸入電平低于Vil時,則認為輸入電平為低電平。

3.輸出高電平(Voh):保證邏輯門的輸出為高電平時的輸出電平的最小值,邏輯門的輸出為高電平時的電平值都必須大于此Voh。

4.輸出低電平(Vol):保證邏輯門的輸出為低電平時的輸出電平的最大值,邏輯門的輸出為低電平時的電平值都必須小于此Vol。

5. 閥值電平(Vt):數字電路芯片都存在一個閾值電平,就是電路剛剛勉強能翻轉動作時的電平。它是一個界于Vil、Vih之間的電壓值,對于CMOS電路的閾值電平,基本上是二分之一的電源電壓值,但要保證穩定的輸 出,則必須要求輸入高電平> Vih,輸入低電平

對于一般的邏輯電平,以上參數的關系如下:

Voh > Vih > Vt > Vil > Vol

6.Ioh:邏輯門輸出為高電平時的負載電流(為拉電流)。

7.Iol:邏輯門輸出為低電平時的負載電流(為灌電流)。

8.Iih:邏輯門輸入為高電平時的電流(為灌電流)。

9.Iil:邏輯門輸入為低電平時的電流(為拉電流)。

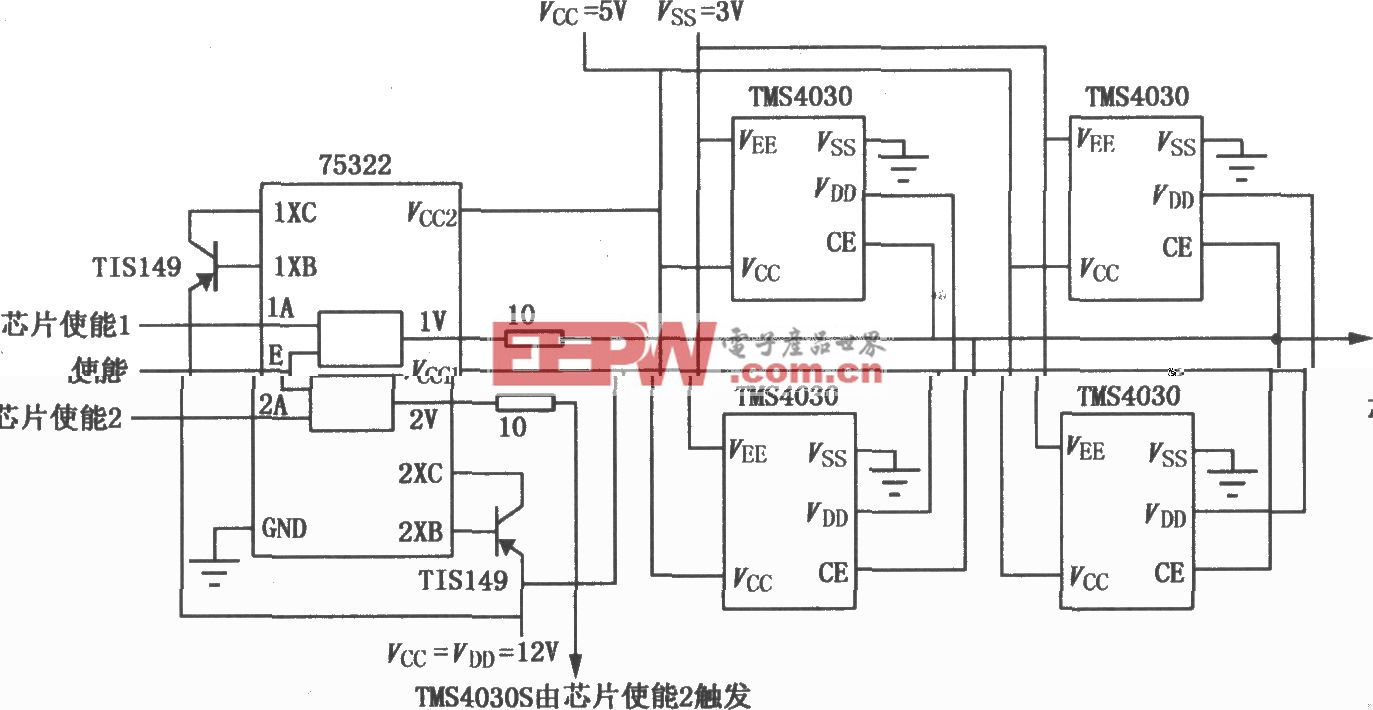

門電路輸出極在集成單元內不接負載電阻而直接引出作為輸出端,這種形式的門稱為開路門。開路的TTL、CMOS、ECL門分別稱為集電極開路(OC)、漏極開路(OD)、發射極開路(OE),使用時應審查是否接上拉電阻(OC、OD門)或下拉電阻(OE門),以及電阻阻值是否合適。對于集電極開路(OC)門,其上拉電阻阻值RL應滿足下面條件:

(1).RL (VCC-Voh)/(n*Ioh+m*Iih)

(2).RL > (VCC-Vol)/(Iol+m*Iil)

其中n:線與的開路門數;m:被驅動的輸入端數。10.常用的邏輯電平

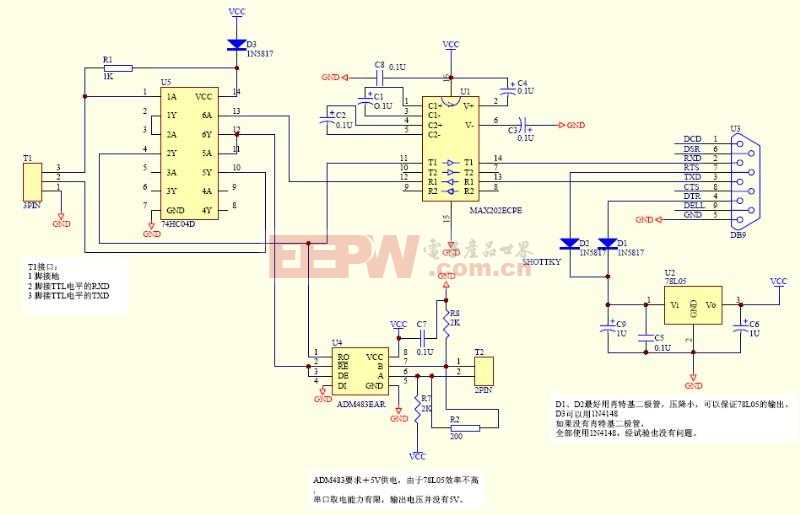

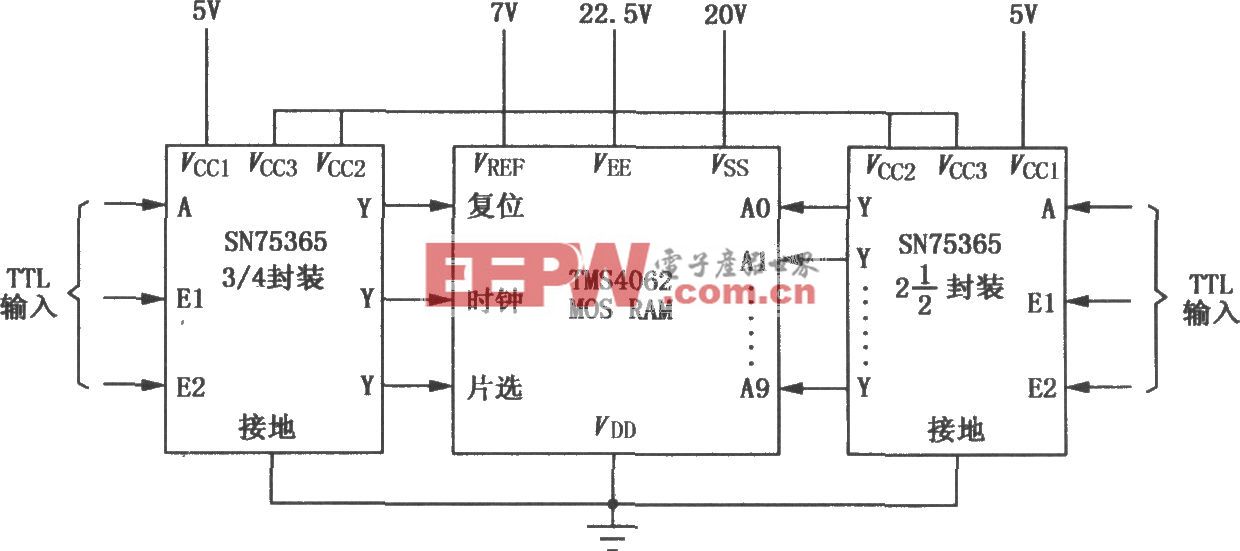

·邏輯電平:有TTL、CMOS、LVTTL、ECL、PECL、GTL;RS232、RS422、LVDS等。

·其中TTL和CMOS的邏輯電平按典型電壓可分為四類:5V系列(5V TTL和5V CMOS)、3.3V系列,2.5V系列和1.8V系列。

·5V TTL和5V CMOS邏輯電平是通用的邏輯電平。

·3.3V及以下的邏輯電平被稱為低電壓邏輯電平,常用的為LVTTL電平。

·低電壓的邏輯電平還有2.5V和1.8V兩種。

·ECL/PECL和LVDS是差分輸入輸出。

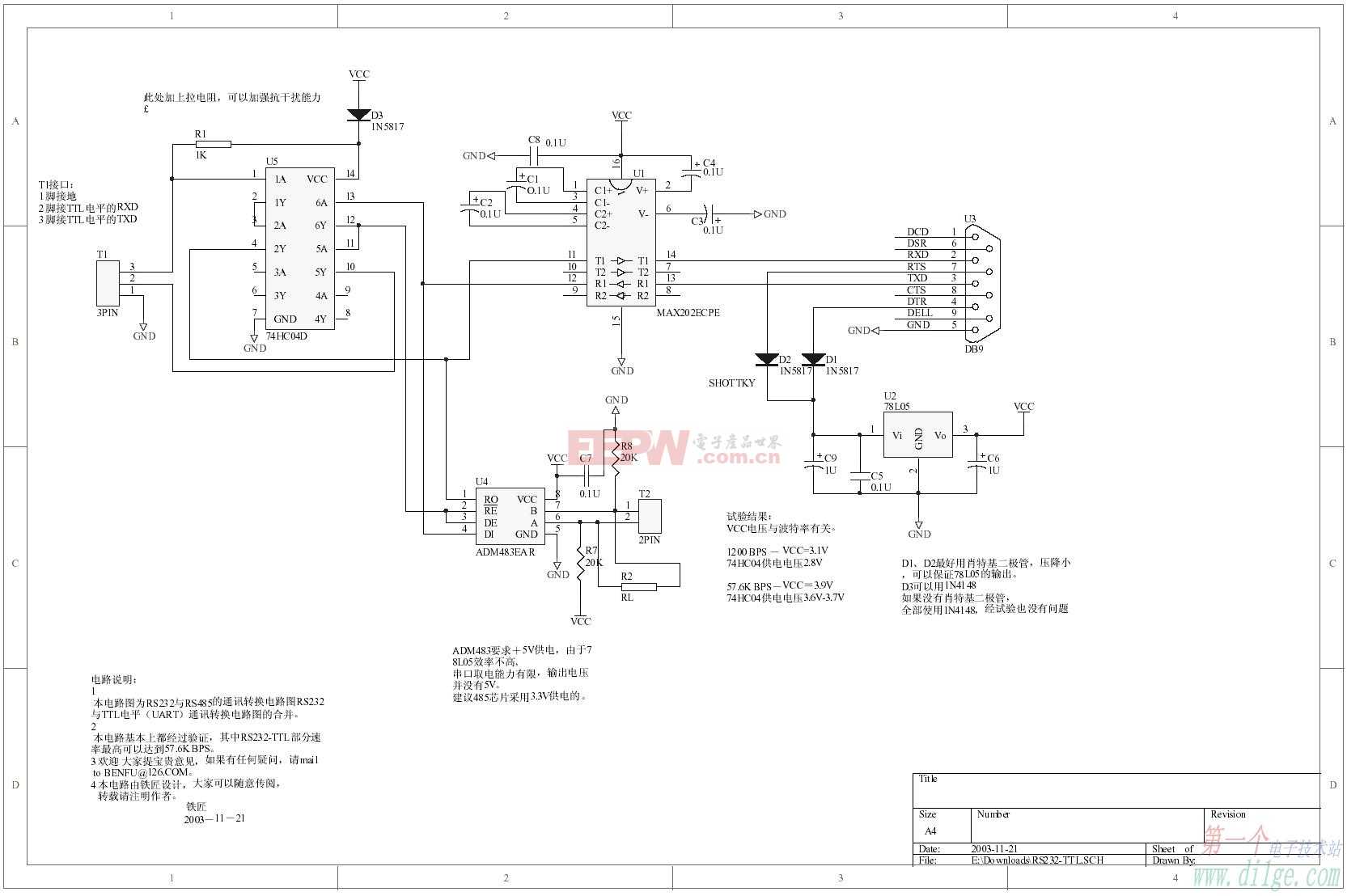

·RS-422/485和RS-232是串口的接口標準,RS-422/485是差分輸入輸出,RS-232是單端輸入輸出。

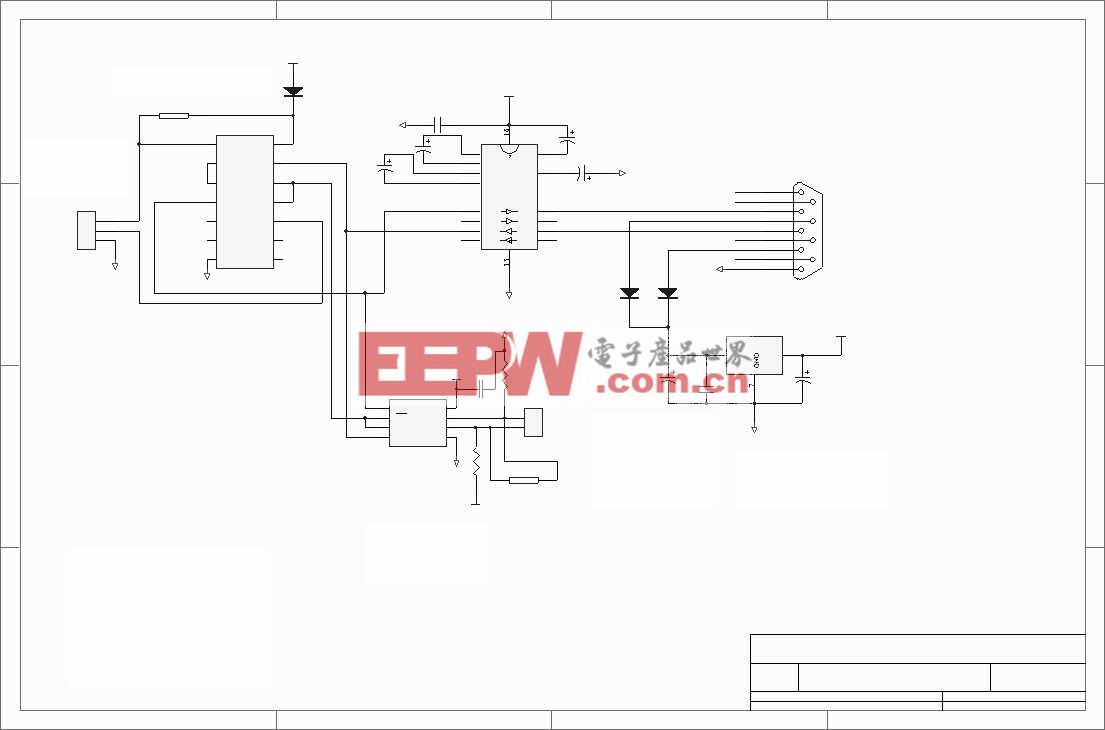

OC門,又稱集電極開路(漏極開路)與非門門電路,Open Collector(Open Drain)。

為什么引入OC門?

實際使用中,有時需要兩個或兩個以上與非門的輸出端連接在同一條導線上,將這些與非門上的數據(狀態電平)用同一條導線輸送出去。因此,需要一種新的與非門電路--OC門來實現“線與邏輯”。

OC門主要用于3個方面:

1、實現與或非邏輯,用做電平轉換,用做驅動器。由于OC門電路的輸出管的集電極懸空,使用時需外接一個上拉電阻Rp到電源VCC。OC門使用上拉電阻以輸出高電平,此外為了加大輸出引腳的驅動能力,上拉電阻阻值的選擇原則,從降低功耗及芯片的灌電流能力考慮應當足夠大;從確保足夠的驅動電流考慮應當足夠小。

2、線與邏輯,即兩個輸出端(包括兩個以上)直接互連就可以實現“AND”的邏輯功能。在總線傳輸等實際應用中需要多個門的輸出端并聯連接使用,而一般TTL門輸出端并不能直接并接使用,否則這些門的輸出管之間由于低阻抗形成很大的短路電流(灌電流),而燒壞器件。在硬件上,可用OC門或三態門(ST門)來實現。 用OC門實現線與,應同時在輸出端口應加一個上拉電阻。

晶體管相關文章:晶體管工作原理

晶體管相關文章:晶體管原理 上拉電阻相關文章:上拉電阻原理

評論