基于VHDL的Petri網系統的FPGA實現

3時延Petri網的實現

3.1時延Petri網的定義

時延PN被用來描述其運行與時間有關的系統。主要有兩種:P時延PN和T時延PN。因二者是等效的,其中一個模型可以轉換成另一個模型,故在此主要實現了T時延PN。

定義2[1]T時延PN是二元組

Tempo是從變遷集T到非負有理數集的函數,Tempo(Tj)=dj是與變遷Tj相聯系的時限,它規定了Petri網中的每一個變遷的持續時間。

在T時延PN中,每個變遷均有一為零或任一正實數的持續時間。而庫所中沒有持續時間,只要和它相連的變遷激發,庫所就可失去或獲得托肯。當變遷的輸入庫所中含有托肯時,變遷是使能的,但要真正激發需要經過一段持續時間。

3.2變遷時化Petri網元件的實現

T時延PN中庫所元件與同步Petri網一致。

T時延PN中變遷元件的實現是在基本Petri網中變遷元件的基礎上設計了一個計時器TIME,如圖2(b),clk為計時頻率,決定了計時的精度;en為其使能端,當變遷可激發時,en為1,計時器開始計時,計時結束時co輸出為1。

在圖2(a)中變遷T與時延D=n相連,當庫所P0和P1中各有一個托肯時,變遷T獲得發生權,但到T發生,需有n個單位的延時.調用元件T_M和計時元件TIME,建立邏輯電路如圖2(c)示,并經過編譯形成圖2(d)所示邏輯模塊時化變遷元件tim。

用VHDL語言實現計時器模塊源程序如下:

if clkevent and clk=1 then

if en=1 then

if q=n then q=0;co=1;else q=q+1; co=0;end if;

else q=0; co=0;end if;end if;

3.3變遷時化Petri網元件實現的應用舉例

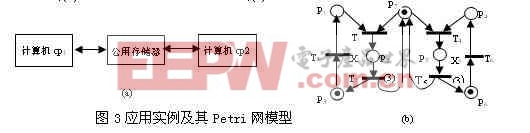

兩臺計算機使用一個公共存儲器,如圖3(a),假設每臺計算機可以有三種狀態:(a)不需要該存儲器;(b)需要存儲器但還沒有使用它;(c)正在使用存儲器。

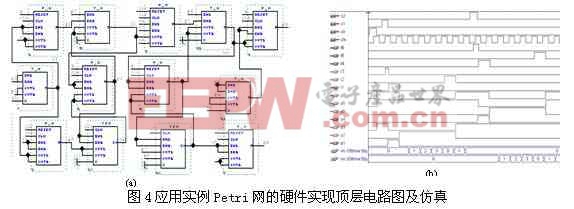

則對其建立Petri網模型如圖3(b)示。各庫所和變遷的含義解釋為:P1,P4分別表示CP1、CP2發出需要該存儲器請求;P2、P5分別表示CP1、CP2占用該存儲器;P3,P6分別表示CP1、CP2不需要該存儲器;P7表示存儲器;變遷中與時間相關的是T2、T5,分別表示cp占用存儲器的時間。這是一個時延Petri網系統。分別調用元件庫中所形成的庫所元件、變遷元件和時延變遷元件,作出該系統的邏輯電路圖如圖4(a),并在EDA軟件Max+PlusⅡ中對其編譯、仿真下載,仿真波形如圖4(b)示。

評論