基于FPGA的高速數(shù)據(jù)傳輸、記錄及顯示系統(tǒng)

1 概述

雷達(dá)數(shù)據(jù)形成分機(jī)具有數(shù)據(jù)量大、傳輸速率高、幀格式固定等特點(diǎn).目前用于雷達(dá)數(shù)據(jù)傳輸的一般有PCI總線和網(wǎng)卡,其中32位的PCI接口數(shù)據(jù)傳輸速率最大可以達(dá)到133Mbit/s,而目前廣泛采用的以太網(wǎng)卡的最大傳輸速率達(dá)到100Mbit/s,雖然這兩者的傳輸速度完全可以滿足要求,但是它們存在安裝繁瑣,受計(jì)算機(jī)插槽數(shù)量和地址、中斷資源限制等弱點(diǎn).USB(Universal Serial Bus)是一種通用串行總線,具有即插即用、可熱插拔,使用方便、成本低的特點(diǎn),其USB1.0能提供12Mbps的全速速率或1.5Mbps的低速速率,而USB2.0 則可以支持480Mbps的高速傳輸速率.因此,在高速數(shù)據(jù)傳輸、記錄及顯示系統(tǒng)中,考慮到需要方便靈活地與計(jì)算機(jī)通信,可采用USB通訊方式來對雷達(dá)數(shù)據(jù)形成分機(jī)進(jìn)行檢測.

2 設(shè)計(jì)方案

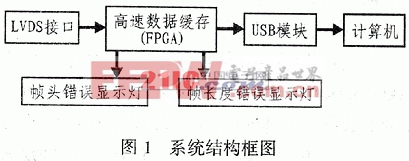

整個系統(tǒng)主要由低電壓差分信號(LVDS)接口電路、基于FPGA的高速數(shù)據(jù)緩存、判斷數(shù)據(jù)錯誤模塊、USB傳輸模塊和計(jì)算機(jī)組成,其系統(tǒng)結(jié)構(gòu)框圖如圖1所示.當(dāng)?shù)碗妷翰罘中盘柦涌陔娐钒呀邮盏睦走_(dá)數(shù)據(jù)形成分機(jī)數(shù)據(jù)送入FPGA緩存后,該信息便可通過USB接口進(jìn)行傳輸、記錄并在計(jì)算機(jī)上顯示.該系統(tǒng)由低電壓差分信號驅(qū)動芯片DS90LV31(發(fā)送器)、 DS90LV32(接收器)、控制芯片XC2V500、USB控制芯片C8051F320、總線驅(qū)動器芯片74HC244組成.

3 系統(tǒng)功能及硬件實(shí)現(xiàn)

本系統(tǒng)主要由低電壓差分信號傳輸接口、FPGA功能模塊和USB傳輸模塊三部分構(gòu)成.

3.1 低電壓差分信號傳輸接口

低電壓差分信號LVDS(Low Voltage Differential Signal)標(biāo)準(zhǔn)是一種用于高速數(shù)據(jù)傳輸?shù)奈锢韺咏涌跇?biāo)準(zhǔn).由于電壓信號擺幅較低,而且可提供電流模式驅(qū)動輸出,因此LVDS 技術(shù)只產(chǎn)生極低的噪音,而且功耗也極低,甚至不論頻率高低,功耗幾乎不變;此外,由于LVDS是以差分方式傳送數(shù)據(jù),因此不易受共模噪音影響.由于具有超高速(1.4Gb/s)串行傳輸、低功耗及低電磁輻射的特性,低電壓差分信號傳輸是在銅介質(zhì)上實(shí)現(xiàn)千兆位級高速通信的優(yōu)先方案,可用于服務(wù)器、可堆壘集線器、無線基站、ATM交換機(jī)及高分辨率顯示等,也可用于通信系統(tǒng)的設(shè)計(jì).美國國家半導(dǎo)體公司的DS90LV31和DS90LV32是高性能的CMOS低功耗、低電壓差分信號驅(qū)動器,采用3.3V供電,可支持大于400Mbps的數(shù)據(jù)率,滿足ANSI/TIA/EIA-644標(biāo)準(zhǔn).其中DS90LV31可實(shí)現(xiàn)四路低電壓TTL信號轉(zhuǎn)低電壓差分信號,而DS90LV32則可實(shí)現(xiàn)四路低電壓差分信號轉(zhuǎn)低電壓TTL信號.

3.2 FPGA功能模塊

本設(shè)計(jì)采用Xilinx公司的FPGAField Pro-grammable gate array,現(xiàn)場可編程門陣列 芯片XC2V500來實(shí)現(xiàn)高速數(shù)據(jù)緩存.XC2V500屬于Vir-tex-II系列,是一種高密度、高性能的FPGA.XC2V500可通過JTAG接口實(shí)現(xiàn)在線編程;它采用0.15m和0.12m混合工藝設(shè)計(jì);內(nèi)核電壓為1.5V,低功耗;可支持多種接口標(biāo)準(zhǔn);內(nèi)部時鐘頻率可達(dá)420MHz;采用專門的在系統(tǒng)可編程PROM芯片18V04進(jìn)行配置.

FPGA的主要功能是高速數(shù)據(jù)緩存及判斷傳輸數(shù)據(jù)幀頭錯誤、幀長度錯誤,具體說明如下:

(1)高速數(shù)據(jù)緩存

雷達(dá)數(shù)據(jù)形成分機(jī)以10MHz的頻率,每秒發(fā)送2000~3000幀、每幀6400字節(jié)的數(shù)據(jù),將如此高速、大量的數(shù)據(jù)進(jìn)行準(zhǔn)確無誤的緩存是本系統(tǒng)的技術(shù)難點(diǎn)之一.本方案將數(shù)據(jù)形成分機(jī)送過來的數(shù)據(jù)先放在FPGA的異步FIFOFirst In First Out 存儲器里,FIFO存儲器同時要有與數(shù)據(jù)形成分機(jī)及USB的接口,且兩接口操作互不干涉,以提高數(shù)據(jù)吞吐率.根據(jù)FIFO存儲器的Full和Empty標(biāo)志可判斷存儲器全滿或空.FIFO存儲器的特點(diǎn)是:不需要地址尋址,可簡化控制信號;數(shù)據(jù)寫入和讀出不依賴于數(shù)據(jù)速率,可以慢寫快讀、也可快寫滿讀;進(jìn)行數(shù)據(jù)寬度和存儲深度的擴(kuò)展不會增加額外的時間延遲,因此滿足了上述要求.

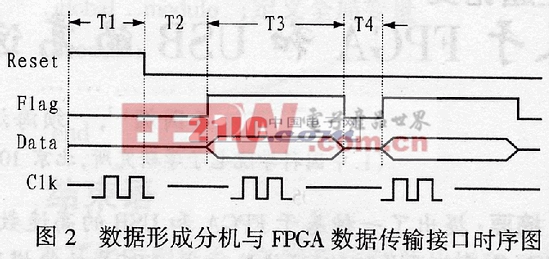

數(shù)據(jù)形成分機(jī)發(fā)送的數(shù)據(jù)包括16 Bit并行數(shù)據(jù)信號Data、數(shù)據(jù)有效標(biāo)志信號Flag、時鐘信號Clk及復(fù)位信號Reset.圖2為數(shù)據(jù)形成分機(jī)與FPGA數(shù)據(jù)傳輸接口時序圖.其中Reset為清零信號,除T1時間外均保持低電平;Flag信號高電平持續(xù)時間為320μs;Clk為10MHz的讀時鐘.FPGA接收到數(shù)據(jù)形成分機(jī)發(fā)來的數(shù)據(jù)有效標(biāo)志信號Flag后,將首先確定數(shù)據(jù)幀頭,然后以10MHz的時鐘頻率Clk讀16 Bit并行數(shù)據(jù)信號Data并存儲在FIFO存儲器中,以等待USB控制芯片取走.

(2)判斷幀數(shù)據(jù)錯誤

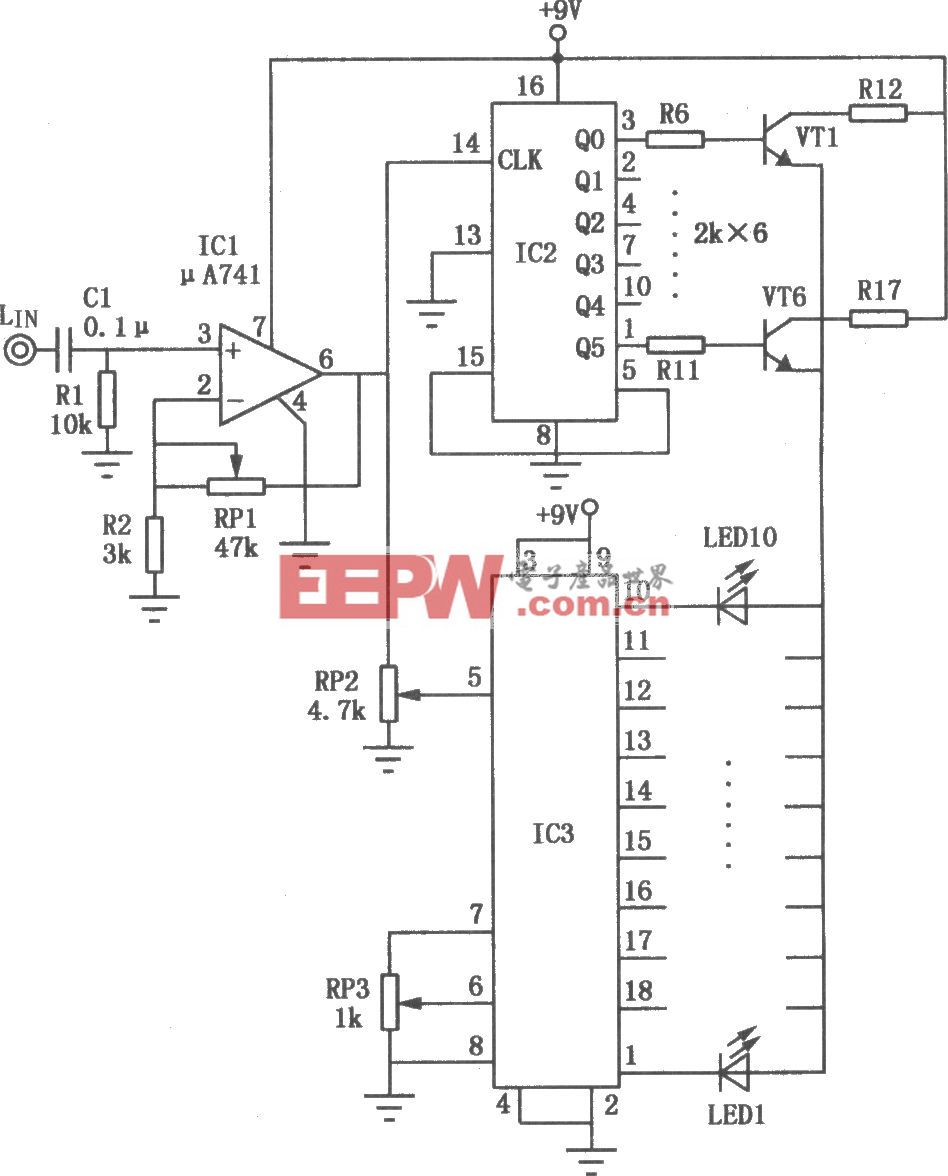

數(shù)據(jù)形成分機(jī)發(fā)送過來的每幀數(shù)據(jù)的幀頭、幀長度是固定的.FPGA對接收的每一幀數(shù)據(jù)都需要判斷幀頭及幀長度是否錯誤.每出現(xiàn)一次錯誤,FP-GA會對其進(jìn)行一次累加,對應(yīng)產(chǎn)生一個脈沖,然后將其用74HC244驅(qū)動后分別接LED顯示燈,就可以二進(jìn)制方式顯示錯誤次數(shù).

3.3 USB傳輸模塊

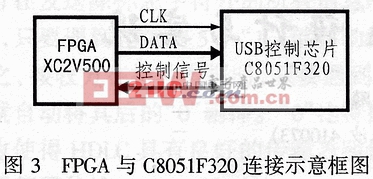

通過USB傳輸模塊可把存在FIFO存儲器里的數(shù)據(jù)傳送給計(jì)算機(jī)并記錄下來,本設(shè)計(jì)采用Cygnal公司的C8051F系列USB控制芯片C8051F320.C8051F320是將微控制器和USB控制器集成在一起的芯片,完全符合USB1.1規(guī)范,最大傳輸速度可達(dá)12Mbps.C0801F320的運(yùn)行指令采用流水線結(jié)構(gòu),機(jī)器周期由標(biāo)準(zhǔn)8051的12個系統(tǒng)時鐘周期降為一個系統(tǒng)時鐘周期,處理能力大大提高.它還內(nèi)嵌JTAG調(diào)試電路,可在系統(tǒng)編程和調(diào)試等.FPGA與C8051F320之間的具體連接控制框圖如圖3所示.

當(dāng)PC機(jī)向C8051F320發(fā)出接收數(shù)據(jù)的命令后,C8051F320便可給FPGA發(fā)控制信號,以使FPGA在下一幀數(shù)據(jù)開始時打開FIFO寫使能;數(shù)據(jù)形成分機(jī)通過寫操作不斷將數(shù)據(jù)存入FIFO存儲器.當(dāng)FIFO存儲器中的數(shù)據(jù)達(dá)到一幀時,Full標(biāo)志有效,向C8051F320請求中斷,并將寫使能關(guān)閉,讀使能打開;C8051F320響應(yīng)中斷后將以CLK時鐘頻率讀FI-FO存儲器中的數(shù)據(jù)DATA;每讀完一幀,FIFO存儲器的讀使能關(guān)閉,寫使能打開,同時接收下一幀數(shù)據(jù),直到PC機(jī)發(fā)停止命令或接收完要求的幀數(shù).

4 軟件設(shè)計(jì)

C8051F320中的8051內(nèi)核不但與MCS-51指令完全兼容,而且Cygnal公司的工具包還為其提供了基于Windows的USB總線驅(qū)動程序和功能驅(qū)動程序,這樣,用戶就可以從煩瑣的驅(qū)動程序開發(fā)中解脫出來,從而大大減少開發(fā)時間、風(fēng)險和成本.

本系統(tǒng)軟件設(shè)計(jì)由兩部分組成:動態(tài)鏈接庫和應(yīng)用程序.動態(tài)鏈接庫負(fù)責(zé)與內(nèi)核的USB功能驅(qū)動程序通信并接收應(yīng)用程序的各種操作請求,而應(yīng)用程序則負(fù)責(zé)對傳輸數(shù)據(jù)進(jìn)行記錄、顯示并實(shí)時顯示數(shù)據(jù)傳輸?shù)臓顟B(tài).

動態(tài)鏈接庫的工作原理如下:當(dāng)它收到應(yīng)用程序的數(shù)據(jù)傳輸請求后,會創(chuàng)建兩個線程:數(shù)據(jù)傳輸線程和記錄、顯示線程.其中數(shù)據(jù)傳輸線程負(fù)責(zé)將數(shù)據(jù)寫到應(yīng)用程序要提交的內(nèi)存;而記錄、顯示線程則負(fù)責(zé)給應(yīng)用程序發(fā)送記錄和顯示消息.當(dāng)應(yīng)用程序接收到此消息后,便從它提交的內(nèi)存中讀取數(shù)據(jù)并存盤和顯示.

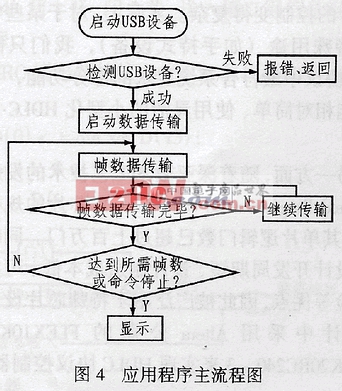

用戶態(tài)應(yīng)用程序的主要功能是開啟或關(guān)閉USB設(shè)備、檢測USB設(shè)備、設(shè)置數(shù)據(jù)傳輸幀數(shù)、通過USB接口傳輸、記錄并顯示數(shù)據(jù)、實(shí)時顯示數(shù)據(jù)傳輸?shù)臓顟B(tài)包括幀數(shù)、字節(jié)數(shù)等,其應(yīng)用程序主流程圖如圖4所示.

本設(shè)計(jì)的應(yīng)用軟件基于Windows系統(tǒng),并采用VC作為軟件開發(fā)環(huán)境,這樣可以利用現(xiàn)有的軟件資源來縮短軟件開發(fā)周期,同時可提供一個友好、美觀清晰、操作簡單的圖形使用界面.訪問USB接口時,調(diào)用Windows API函數(shù)能及時方便地與系統(tǒng)的USB控制芯片進(jìn)行通信,并且可以將傳輸來的數(shù)據(jù)保存并顯示在計(jì)算機(jī)上.

5 結(jié)束語

本文設(shè)計(jì)的基于FPGA和USB的高速數(shù)據(jù)傳輸、記錄系統(tǒng)不但具有體積小、功耗低、成本低、使用靈活方便、硬件電路簡單、可在線更新等特點(diǎn);而且還充分利用了微機(jī)的資源,因而易開發(fā)且擴(kuò)展性好.目前,本系統(tǒng)已投入實(shí)際應(yīng)用之中,基本能達(dá)到高速數(shù)據(jù)傳輸、記錄及顯示的要求,具有較高的實(shí)用價值.

評論