AES算法中S-box和列混合單元的優化及FPGA實現

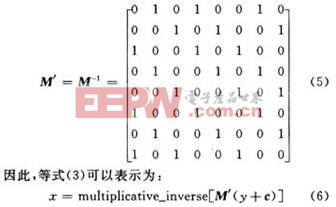

最后,必須找到M-1,即矩陣M的有限域逆矩陣。由有限域逆矩陣的運算方法可知,可以計算出矩陣M的逆矩陣,命名為M’,如式(5)所示:

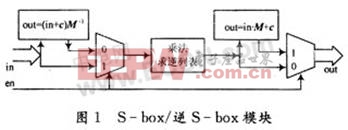

在式(1)和式(6)中,只使用了一個普通的look-up列表,從而將S-box和逆S-box集成,大大減少了字節替代和逆字節替代的硬件需求。圖1展示了集成的S-box/逆S-box模塊,可應用于AES的加密和解密。

1.2 S-box單元中乘法求逆電路的優化

由第1.1節可知,S-box盒的生成電路由加密仿射電路(實現out=(in+c)M-1等式功能),解密仿射電路(實現out=in·M+c等式功能)以及乘法求逆電路三個模塊組成。要減少組合邏輯的復雜度,需要對乘法求逆電路進行優化。下面說明求逆電路的優化過程。

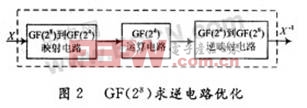

S-box硬件實現時的主要部件是乘法求逆。在有限域GF(28)上,乘法求逆是一種相當復雜的函數,直接在域GF(28)上生成S-box盒,組合邏輯復雜度高,會使電路中邏輯電路的門數大大增加。根據有限域的性質,利用域GF(28)與GF[(24)2]的同構變換,把GF(28)上的求逆轉化在GF[(24)2]上的求逆運算,從而生成S-box單元,可以降低邏輯關系運算的復雜度,優化S-box的面積。

所采用有限域GF(28)上的乘法求逆電路模塊優化過程如圖2所示。優化的乘法求逆過程可表述如下:

(1)通過線性變換T將GF(28)的輸入X映射到域GF(24)上的元素b,c;

(2)構建相應的域GF(24)的一次多項式,定義域GF(24)上的加法、乘法和求逆運算。利用域GF(24)上的加法、乘法和求逆運算,得到域GF(24)上元素b,c的逆元素p,q;

(3)構建線性變換T-1,將域GF(24)上的元素p,q映射到域GF(28)上,得到域GF(28)上的元素x的逆元素y=T-1(p,q)。

評論