混合邏輯電平的接口技術

在功耗低、體積小的便攜式設備(蜂窩電話、PDA、筆記本電腦、數字相機等)的應用需求驅動下,越來越多的半導體器件采用低電壓設計技術,很多半導體器件制造廠家紛紛推出3.3V和2.5V等一系列超低功耗集成電路。這樣使很多低電壓邏輯標準得以廣泛應用。在新一代的銀行終端、教育終端等產品的設計過程中,為了降低成本、保持與終端外設的兼容性,還需要在同一系統中采用許多不同邏輯標準的器件,因此在同一系統中不可避免地存在不同供電電壓的模塊。如何解決不同的邏輯電平信號間的接口問題,就成了硬件工程師面臨的關鍵技術。本文結合TFT彩色液晶網絡終端的設計,詳細介紹了幾種邏輯電平信號的接口特性,并討論了它們之間的接口技術。

1DC/DC電源變換

傳統的線性穩壓器,如LM117系列都要求輸入電壓比輸出電壓高3V以上,否則不能正常工作,同時傳統的線性穩壓器轉換效率低,發熱量大,所以LM117系列已經不能滿足低功耗小體積的應用系統的電源設計要求。電池供電的便攜式設備,對于電源轉換效率和散熱要求更高,所以必須尋求其他的解決方案。

TFT彩色液晶網絡終端主板涉及大量的5.0V和3.3V邏輯信號,必須有5.0V和3.3V兩個供電模塊。為了與其它系列終端的外置電源兼容,這里采用國家半導體公司的LM2576從12V變換到5V,再采用MICREL公司的MIC5207(或Linear公司的LT1086)從5V變換到3.3V。

LM2576是基于開關電源技術的低電壓輸出單片集成電路,內置52kHz的振蕩電路,僅僅需要4個外圍器件,電源轉換效率高達77%,輸出電流最大可達3A,發熱量小,電磁輻射小,可靠性高。

面對低電壓電源的需求,許多電源芯片公司推出了低壓差線性穩壓器LDO(LowDropoutRegulator)。這種電源芯片的壓差可以低至0.2V~1.3V,可以實現5V轉3.3V/2.5V、3.3V轉2.5V/1.8V等要求。生產LDO的公司很多,如ALPHA、LT(LinearTechnology)、NI(Nationalsemiconductor)、TI等。低壓差線性穩壓器MIC5207特別適合手持的電池供電設備,它有一個與COMS、TTL電平兼容的使能控制引腳,便于關斷電源降低功耗,其外圍電路也特別簡單。

2各種邏輯電平信號的電特性

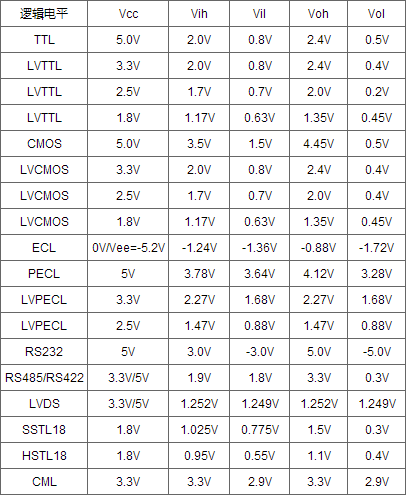

在TFT彩色液晶網絡終端系統中,中央處理器IntelPXA255的I/O端口是3.3V的CMOS結構;USBHost控制器SL811HS的I/O端口是3.3V的CMOS結構?熏兼容TTL電平;超級I/O控制器W83977ATF具有5.0VCMOS和5.0VTTL兩種I/O端口。它們的電平特性如表1所示。遵守同一邏輯電平標準的不同器件,端口的電特性可能略有不同,即使是同一器件,在不同環境下表現出的電特性也是不同的,所以在設計電路時,一定要具體情況具體分析。

表1中,VOH表示輸出高電平的最小值;VOL表示輸出低電平的最大值。表1VIH表示輸入高電平的最小值;VIL表示輸入低電平的最大值。表1列出了器件的常見電特性,有些集成電路略有差別。

銀行終端需要外接的串口設備多達8個以上,所以解決RS-232C串口與3.3V和5.0V邏輯電平接口也是TFT彩色液晶網絡終端系統的一項重要技術(實達電腦公司有些終端的串口是TTL電平)。

RS-232C標準是美國EIA(電子工業聯合會)與BELL等公司一起開發的、于1969年公布的通信協議,全稱是EIA-RS-232C。它適于數據傳輸速率在0~20000bps的通信。這個標準對串行通信接口的有關問題,如信號線功能、電特性都作了明確規定。由于通信設備廠商都生產與RS-232C制式兼容的通信設備,因此,它作為一種標準,目前已在微機通信接口中廣泛采用。

RS-232C采用負邏輯,規定+3V~+15V任意電壓表示邏輯0(或信號有效),-3V~-15V任意電壓表示邏輯1(或信號無效)。

目前生產TFT液晶顯示屏的廠家主要有LG.PHILIPS、SAMSUNG、SHARP、NEC等。這些顯示屏,有的是TTL電平接口,有的是LVDS接口。使用TTL電平接口,其有效距離僅為50cm?鴉如果是3.3V電平,傳輸距離更短。在終端應用中,一般是顯示屏與主機結合為一體,但是也有顯示屏遠離主機的情況,所以這里簡要介紹一下LVDS信號。目前LVDS技術在傳輸距離上有其局限性,一般應用在20m以下。

LVDS(LowVoltageDifferentialSignaling)是一種小振幅差分信號技術,使用非常低的幅度信號(約350mV)通過一對差分PCB走線或平衡電纜傳輸數據。LVDS在兩個標準中定義:IEEEP1596.3(1996年3月通過),主要面向SCI(ScalableCoherentInterface);ANSI/EIA/EIA-644(1995年11月通過),主要定義了LVDS的電特性,并建議了655Mbps的最大速率和1.823Gbps的無失真媒質上的理論極限速率。在兩個標準中都指定了與物理媒質無關的特性,這意味著只要媒質在指定的噪聲邊緣和歪斜容忍范圍內發送信號到接收器,接口都能正常工作。

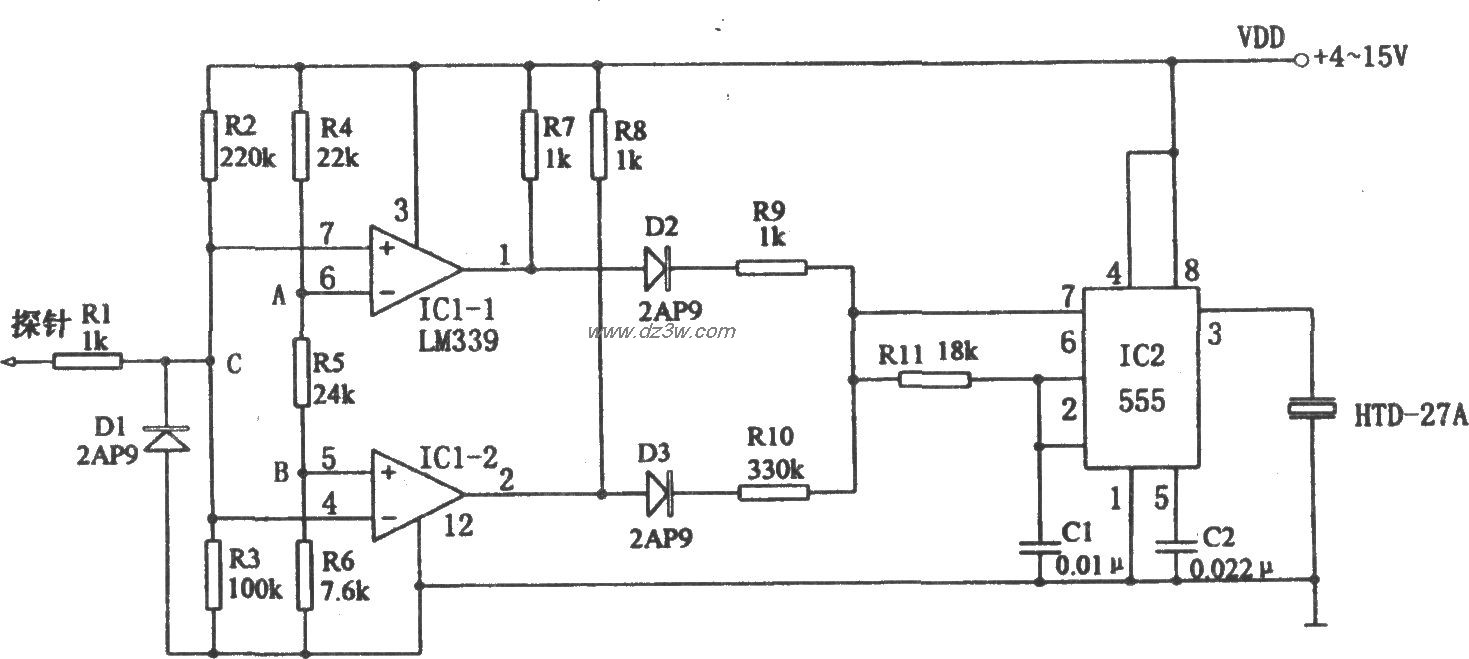

圖1為LVDS的原理簡圖,其驅動器由一個恒流源(通常為3.5mA)驅動一對差分信號線組成。在接收端有一個高的直流輸入阻抗(幾乎不會消耗電流),所以幾乎全部的驅動電流將流經100Ω的終端電阻在接收器輸入端產生約350mV的電壓。當驅動狀態反轉時,流經電阻的電流方向改變,于是在接收端產生一個有效的“0”或“1”邏輯狀態。

LVDS技術的恒流源模式低擺幅輸出意味著LVDS具有很高的傳輸速度,能較好地抑制共模信號,并行的差分信號降低了周圍的電磁干擾,CMOS工藝保證了較低的靜態功耗。另外,由于是低擺幅差分信號技術,其驅動和接收不依賴于供電電壓,因此,LVDS能比較容易應用于低電壓系統中,如3.3V甚至2.5V,保持同樣的信號電平和性能。LVDS也易于匹配終端。無論其傳輸介質是電纜還是PCB走線,都必須與終端匹配,以減少不希望的電磁輻射,提供最佳的信號質量。通常,一個盡可能靠近接收輸入端的100Ω終端電阻跨在差分線上即可提供良好的匹配。

評論