信號邏輯電平標準詳解

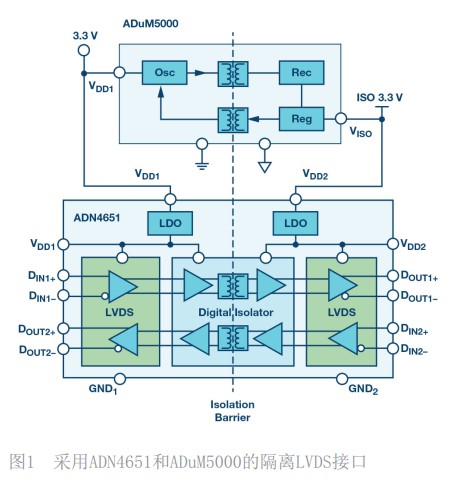

信號的邏輯電平經歷了從單端信號到差分信號、從低速信號到高速信號的發展過程。最基本的單端信號邏輯電平為CMOS、TTL,在此基礎上隨著電壓擺幅的降低,出現LVCMOS、LVTTL等邏輯電平,隨著信號速率的提升又出現ECL、PECL、LVPECL、LVDS、CML等差分信號邏輯電平。

本文引用地址:http://www.czjhyjcfj.com/article/201609/296860.htm1.信號邏輯電平參數概念定義

邏輯電平是指數字信號電壓的高、低電平,相關參數定義如下:

(1)輸入高電平門限Vih:保證邏輯門的輸入為高電平時所允許的最小輸入高電平,當輸入電平高于Vih時,則認為輸入電平為高電平;

(2)輸入低電平門限Vil:保證邏輯門的輸入為低電平時所允許的最大輸入低電平,當輸入電平低于Vil時,則認為輸入電平為低電平;

(3)輸出高電平門限Voh:保證邏輯門的輸出為高電平時的輸出電平的最小值,邏輯門的輸出為高電平時的電平值都必須大于此Voh;

(4)輸出低電平門限Vol:保證邏輯門的輸出為低電平時的輸出電平的最大值,邏輯門的輸出為低電平時的電平值都必須小于此Vol;

(5)閾值電平Vt:數字電路芯片都存在一個閾值電平,就是電路剛剛勉強能翻轉動作時的電平。它是一個介于Vil、Vih之間的電壓值;對于CMOS電路的閾值電平,基本上是二分之一的電源電壓值,但要保證穩定的輸出,則必須要求輸入高電平>Vih,輸入低電平 < Vil。

Tips:閾值電平只是用來表征數字電路芯片的特性,實際硬件電路設計過程中具有實際意義的是Vih和Vil。

對于一般的邏輯電平,Vih、Vil、Voh、Vol以及Vt的關系為:Voh>Vih>Vt>Vil >Vol

(6)Ioh:邏輯門輸出為高電平時的負載電流(為拉電流);

(7)Iol:邏輯門輸出為低電平時的負載電流(為灌電流);

(8)Iih:邏輯門輸入為高電平時的電流(為灌電流);

(9)Iil:邏輯門輸入為低電平時的電流(為拉電流)。

2.常見信號邏輯電平參數

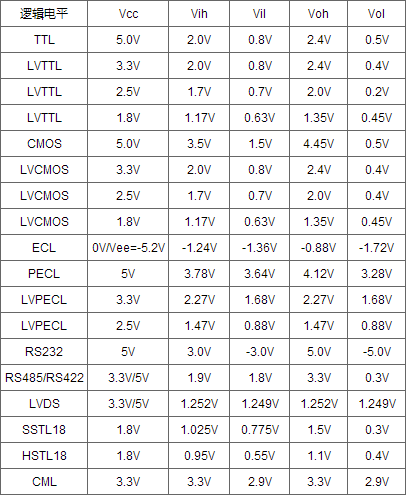

常用的邏輯電平有:TTL、CMOS、ECL、PECL、LVDS、LVPECL、RS232、RS422、RS485、CML、SSTL、HSTL等。

(1)TTL和CMOS的邏輯電平按典型電壓可分為四類:5V系列、3.3V系列、2.5V系列和1.8V系列,3.3V的TTL電平和CMOS電平通常稱為LVTTL和LVCMOS;

(2)RS232/RS422/RS485是串口(UART)的電平標準,RS232是單端輸入輸出,RS422和RS485是差分輸入輸出;

(3)ECL、PECL、LVPECL、LVDS、CML是差分輸入輸出電平;

(4)SSTL主要用于DDR存儲器,HSTL主要用于QDR存儲器;

電平通常標準參數如下表所示,具體芯片建議參考Datasheet。

由上表可見,常用的差分信號電平標準LVPECL、LVDS、CML的輸入和輸出端具有相同的門限參數。這是由產生差分信號的硬件結構決定的,下一期將進行詳細說明。

評論