流水線型ADCMAX1200及其與DSP的接口

摘要:新型的流水線結構模數轉換技術是實現高速、高精度、低功耗的數據轉換的新技術。介紹16位MAX1200的結構、原理及其在高速數據采集系統中與DSP的接口及應用,可對流水線型ADC有實頻了解。

1 概述

為了適應計算機、通信和多媒體技術的飛速發展以及高新技術領域的數字化進程不斷加快,ADC在工藝、結構、性能上都有了很大進步,正在朝著低功耗、高速、高分辨率的方向發展。新型的流水線結構是實現高速低功耗ADC的新型有效的方法。MAX1200就是采用這一新技術的高速、高精度、低功耗ADC的代表。

*單電源+5V供電;

*±VREF差分輸入,正向參考電壓RFPF由外部+4.906V電壓基準提供,負向參考電壓RFNF接至模擬地;

*輸入信號fin=100kHz時,非雜散動態范圍為91dB;

*1Msps,+5V供電時功耗273mW;

*±0.5LSB差分非線性誤差;

*三態、二進制補碼輸出;

*快速、可控自校準功能;

*44腳MQFP封裝。

表1為引腳說明

表1 引腳說明

| 引腳號 | 引腳名稱 | 說 明 |

| 1 | ST_CAL | 自校準觸發數字輸入端 ST_CAL=0,正常轉換;ST_CAL=1,啟動自校準功能 |

| 2、4、5 | AGND | 模擬地 |

| 3、6 | AVDD | 模擬電源+5(1±0.05)V |

| 7 | DOR | 數據溢出位 |

| 815 | D15D8 | 輸出數據高8位 |

| 16 | DRVDD | 驅動輸出的數字電源,+3~+5.25V,必須保證DRVDD≤DVDD |

| 17、28、29 | DGND | 數字地 |

| 18~25 | D7D0 | 輸出數據低8位 |

| 26 | TEST1 | 測試1腳,不接 |

| 27、30 | DVDD | 數字電源,+3~+2.25V |

| 31 | CLK | 輸入時鐘,AVDD獲取能量可避免抖動 |

| 32 | DAV | 數據有效時鐘,通過此時鐘控制,數據可傳送到存儲器或其它任何數據接收系統 |

| 33 | OE | 輸出使能 0E=0,D0~D15為高阻態;OE=1,D0~D15使能 |

| 34 | TEST0 | 測試0腳 |

| 35 | CM | 普通模式電壓。模擬輸入,用來驅動介于正負參考電壓的中間值 |

| 36 | RFPF | 正參考電壓,強制輸入 |

| 37 | RFPS | 正參考電壓,敏感輸入 |

| 38 | RFNF | 負輸入電壓,強制輸入 |

| 39 | FPNS | 負參考電壓,敏感輸入 |

| 40 | INP | 正輸入端 |

| 41、42 | NC | 不接 |

| 43 | INN | 負輸入端 |

| 44 | END_CAL | 校準結束標志位 END_CAL=0,校準正在=1,正常轉換 |

2 工作原理

流水線型(pipeline)ADC又稱為子區式ADC,由級聯的若干級電路組成。每一級包括1采樣/保持放大器,1個低分辨率持ADC和DAC,以及1個求和電路,其中求和電路包括可提供增益的級間放大器。快速精確的n位轉換器分為兩段以上的子區(流水線)來完成。每級電路的采樣/保持器對輸入信號取樣后,先由1個m位分辨率的粗A/D轉換器對輸入進行量,接著用1個至少n位精度的乘積型數模轉換器(MDAC)產生1個對應于量化結果的模擬電平送至求和電路,求和電路從輸入信號中減掉此模擬電平,并將差值精確放大某一固定增益后送交下一級電路處理。經過各級這樣的處理后,最后由1個較高精度的k位細A/D轉換器對殘余信號進行轉換。將上述各級粗、細A/D的輸出組合起來構成高精度的n位輸出;同時必須滿足以下不等式,以便糾正重疊錯誤:

l·m+k>n

其中,l為級數,m為各級中ADC的粗分辨率,k為精細ADC的細分辨率,而n是流水線ADC的總分辨率。圖1所示為MAX1200的4級流水線ADC的原理圖及每級內部結構圖。

圖1中m=8,l=4,n=16。由于采用的開關電容流水線結構中存在開關電容之間的失配問題,所以整個電路的精度由校正和校準邏輯控制。流水線結構的4個采樣過程在輸入信號被采樣和數據輸出到D15~D0之間引入的等待時間,也就是流水線的延遲時間;但是,在連續采樣的情況下可以獲得連續的輸出,只是輸出數據是前面的采樣輸出。時序如圖2所示。

總地來說,流水線ADC不但簡化了電路設計,還具有如下優點:

①每一級的冗余位優化了重疊誤差的糾正,具有良好的線性和低失調;

②每一級具有獨立的采樣/保持放大器,前一級電路的采樣/保持可以釋放出來用于處理下一次采樣,因此,允許流水線各級同時對多個采樣進行處理,從而提高了信號的處理速度,典型的為Tconv100ns。

③功耗低;

④很少有比較器進入亞穩態,從根本上消除了火花碼和氣泡,從而大大減少了ADC的誤差;

⑤多級轉換提高了ADC的分辨率。

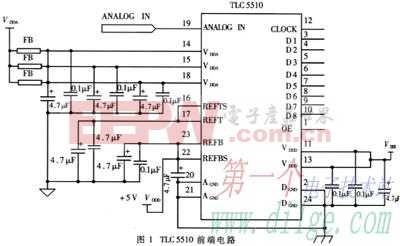

(1)輸入模擬信號

全差分的開關電容電路(SC)用來控制參考電壓和模擬輸入,如圖3所示。采用差分輸入信號比單端輸入具有更好的THD和SFDR性能,并且具有兩倍的信號量程、普通模式下的抗干擾性提高、有效地消除偶次諧波、對輸入信號的放大器預處理要求不高等優點。如果使用單端輸入,負輸入引腳INN連接到普通模式電壓引腳CM上,輸入模擬信號接正輸入端INP。為了充分利用ADC的直到奈奎斯特頻率的優良的AC特性,應盡量采用差分輸入方式。可以通過電路轉換將單端輸入轉換成差分輸入。如圖4所示,利用低噪聲、寬帶的運算放大器MAX4108可以保證MAX1200輸入信號在全功率帶寬范圍的信號純凈。為提高信噪比減小信號失真,在輸入信號進入ADC之前,可采用低通或帶通濾波器調理輸入信號。通常對于低頻輸入信號(100kHz)可采用有源濾波器,高頻輸入信號則采用無源濾波器。

(2)參考電壓

選擇低噪聲的參考電壓可以提高良好的負載穩定性和低的溫度漂移。MAX1200的參考電壓驅動大約1kΩ的片上電阻和21pF的開關電容。為了滿足動態特性的要求,參考電壓要在一個時鐘周期內穩定在0.0015%,因而要設計恰當的驅動電路,如圖5所示。參考電壓也可采用單端輸入或圖3所示的差分輸入,參考電壓不可高于模擬電壓AVDD或低于地。參考電壓引腳處的電容用來提供每一時鐘周期內的動態電荷,這些電容必須具有低的電解質吸收性能;運算放大器MAX410可以保證參考信號的精度。通常典型的正參考電壓RFPF可由4.096V的驅動電壓基準(如MAX6341)提供,負參考電壓可直接和模擬地相連,這樣可達到最佳的信噪比。如果系統對THD性能的要求比SNR更為重要,那么可選擇差分電壓VRFPS=+3.5V,VRENS=+1.5V。普通模式電壓引腳CM對ADC的性能影響很大,采用VCM=(VRFPS+VRFNS)/2,可以保證有很好的動態性能。圖5所示VCM可采用分壓得到。

(3)時鐘

流水線型ADC通常需要50%占空比的時鐘,MAX1200采用圖6所示的電路來產生所需的時鐘。

在這里,時鐘發生器與信號源要有匹配的頻率范圍、振幅、壓擺率。如果輸入信號的壓擺率很小,那么,時鐘抖動可以忽略;如果信號的壓擺率很高,則時鐘的抖動應該限制到最小。因為,對于全振幅輸入的正弦波可能達到的最大信噪比取決于時鐘的抖動:

采用圖6所示的低噪聲和低相位噪聲的信號發生器,可以獲取需要的時鐘。

(4)校標功能

流水線操作采用低分辨率的乘積型數模轉換器(MDAC),其內部的開關電容存在失配問題,因而MAX1200的精度受限于MDAC的精度。MAX1200具有自校準功能,可將電容之間的失配情況進行計算并存儲在片上存儲器中,以便應用于對輸入信號的校準中。在校準過程中,首先,時鐘必須連接工作,ST_CAL由一最小寬度為4倍時鐘周期但不超過17 400個時鐘周期的正脈沖觸發,可與時鐘開行輸入。當ST_CAL觸發1~2個時鐘周期后,END_CAL變為低電平并保持到校準結束。在這一期間參考電壓必須保持穩定在0.01%,否則校準是無效的。在校準過程中,模擬輸入INP和INN一般不接入信號,但如果接入靜態輸入可以獲得更好的校準性能。一旦END_CAL變高則意味著校準結束,此時ADC進入模數轉換狀態。具體時序如圖7的慰。校準結束后,MAX1200對電源±5%的變化或溫度的變化都不敏感,但當溫度變化超過±20℃時則需要重新校準。

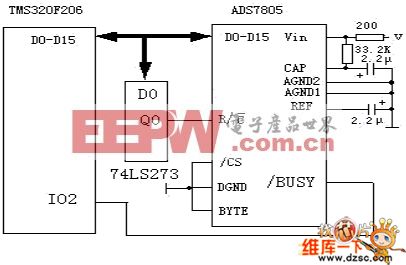

3 MAX1200與DSP的接口

這里,采用美國TI公司的TMS320F206(以下簡答F206)。F206是一種低價格、高性能16位定點DSP,目前已廣泛應用于圖形圖像處理、語音處理、儀器儀表、通信、多媒體及軍事等領域。F206運算速度較快(可達40MIPS),功能較強,源代碼與'C1x、'C2x兼容,且與'5x向上兼容,片內外設向TMS320C5x靠攏。其內部采用程序和數據分開的哈佛結構,具專門的硬件乘法器,采用了四級流水線操作,提供了特殊的DSP指令,可以快速實現各種處理算法。圖8為MAX1200的外圍電路及與F206的接口電路。

下面給出應用DSP進行ADC數據采集的程序:

.title "MAX1200 ADC";標題

.copy "init.h" ;變量和寄存器定義

.copy "vector.h" ;矢量標號定義

.text ;代碼段

F206系統初始化

start:clrc cnf ;映射塊B0到數據存儲區

ldp #0h ;頁指針設置為0

setc intm ;關中斷

splk #0000h,60h

out 60h,wsgr ;設置0等待周期

*設置中斷*

splk #0ffffh,ifr ;中斷標志復位

splk #0001h,imr ;設置INT1中斷有效

splk #0010h,60h

out 60h,icr ;設置中斷模式

*設置IO口輸入輸出狀態*

splk #0c004h,60h ;設置IO2為輸出,IO3為輸入

out 60h,aspcr

*設置從ADC的接收數據存放位置及數據長度*

lar ar1,#rxbuf ;接收數據從0300h單元開始存放

lar ar0,#size ;接收數據長度0020h個數據

mar *,ar1 ;設置AR1為當前輔助寄存器

*控制ADC的OE,啟動自動校準,等待校準完畢后接收數據*

splk #00f4h,61h

out 61h,iosr ;設置ST_CAL=,啟動ADC自動校準

in 62h,iosr ;等待自動校準完畢

bit 62h,8

wait:bcnd wait,ntc ;自動校準正在進行

clrc tc ;自動校準完畢,清除TC

clrc intm ;打開總中斷

loop:idle

b loop;

*INT1中斷服務程序——接收、存儲數據*

inpt1:in *+,000h ;接收數據并存儲到輔助寄存;器所指示數據存儲單元

mar *,ar0

banz skip,ar1

lar ar1,#rxbuf

lar aro,#size

skip:clrc intm

ret

.end ;程序結束

4 小結

利用流水線型ADC可以實現高速精度的模數轉換,這一技術是新型ADC的代表。MAX1200的原理特性及其與DSP的配合使用,可將高速、高精度、低功耗的數字采集系統廣泛地應用于數字通信、高分辨率圖像系統、掃描儀等各種數字化系統中。

評論